# ACE User Guide (UG070)

Achronix Tool Suite

### Copyrights, Trademarks and Disclaimers

Copyright © 2024 Achronix Semiconductor Corporation. All rights reserved. Achronix, Speedcore, Speedster, and ACE are trademarks of Achronix Semiconductor Corporation in the U.S. and/or other countries All other trademarks are the property of their respective owners. All specifications subject to change without notice.

#### Notice of Disclaimer

The information given in this document is believed to be accurate and reliable. However, Achronix Semiconductor Corporation does not give any representations or warranties as to the completeness or accuracy of such information and shall have no liability for the use of the information contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document and the information contained herein at any time and without notice. All Achronix trademarks, registered trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

#### Achronix Semiconductor Corporation

2903 Bunker Hill Lane Santa Clara, CA 95054 USA

Website: www.achronix.com E-mail : info@achronix.com

## **Table of Contents**

| Chapter 1 : Pr | eface                                                   | 1  |

|----------------|---------------------------------------------------------|----|

| Pre            | eface                                                   | .1 |

|                | About This Guide                                        | .1 |

|                | Related Documents                                       | .1 |

|                | Conventions Used in this Guide                          | .2 |

| Chapter 2 : Ge | etting Started                                          | 3  |

| Int            | roduction                                               | 3  |

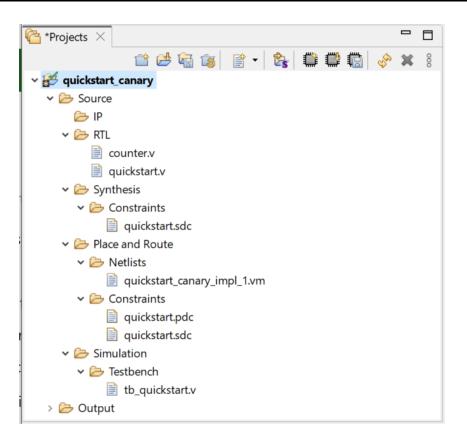

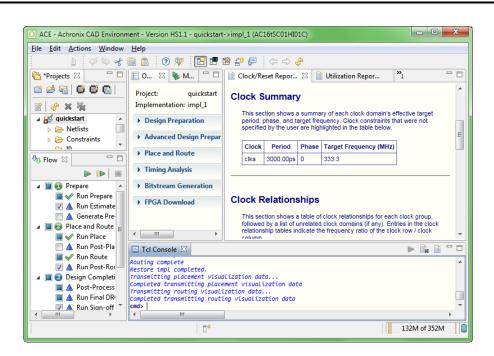

| AC             | E Quickstart Tutorial                                   | 3  |

|                | 1. Create your Project                                  | .3 |

|                | 2. Add your Design Files and Set Implementation Options | .4 |

|                | 3. Run the Flow                                         | .4 |

|                | 4. Analyze the Results                                  | .5 |

|                | Congratulations!!!                                      | .5 |

| Chapter 3 : Co | oncepts                                                 | 6  |

| We             | orkbench                                                | 6  |

| Pe             | rspectives                                              | 6  |

|                | Projects Perspective                                    | 6  |

|                | Floorplanner Perspective                                | .7 |

|                | IP Configuration Perspective                            | .7 |

| U       | IG  | )7   | 0      |

|---------|-----|------|--------|

| $\circ$ | C C | ,,,, | $\sim$ |

| 2D NoC Performance Perspective                                    |    |

|-------------------------------------------------------------------|----|

| Programming and Debug Perspective                                 |    |

| HW Demo Perspective                                               |    |

| Editors                                                           | 9  |

| HTML Report Browser                                               | 9  |

| Text Editor                                                       | 10 |

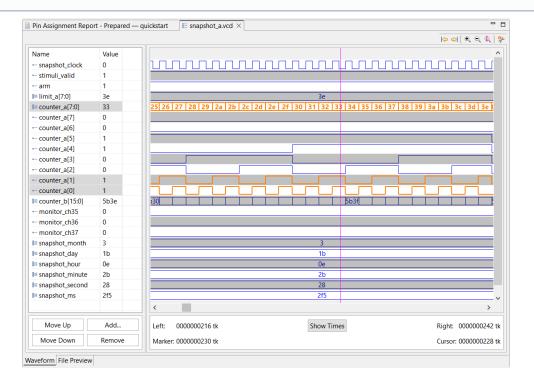

| VCD Waveform Editor                                               |    |

| VCD Viewer Preferences                                            |    |

| Views                                                             | 16 |

| Clock Domains View                                                | 21 |

| Organizing Table Data                                             | 23 |

| Drag-and-Drop                                                     | 25 |

| Clock Regions View                                                |    |

| Using the Table to Display Clock Regions in the Floorplanner View |    |

| Organizing Table Data                                             |    |

| Partial Reconfig Cluster Value                                    |    |

| Clusters View                                                     |    |

| Using the Table to Display Clusters in the Floorplanner View      |    |

| Organizing Table Data                                             |    |

| Partial Reconfig Cluster Value                                    |    |

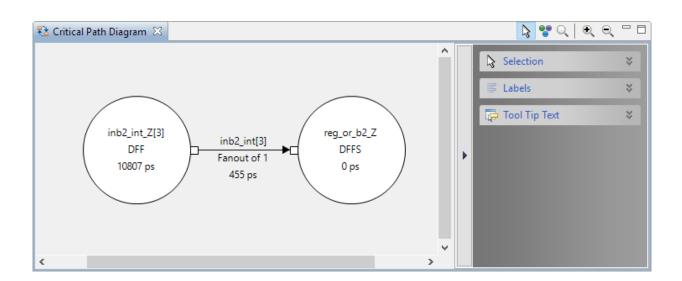

| Critical Path Diagram View                                        |    |

| Fly-Out Palette                                                   |    |

| Critical Paths View                                               |    |

| Download View                                                     |    |

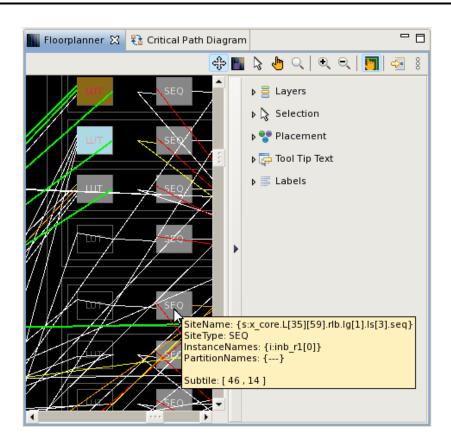

| Floorplanner View                                                 |    |

| Panning and Zooming                                               |    |

| Fly-Out Palette                 |    |

|---------------------------------|----|

| Flow View                       |    |

| HW Demo View                    | 60 |

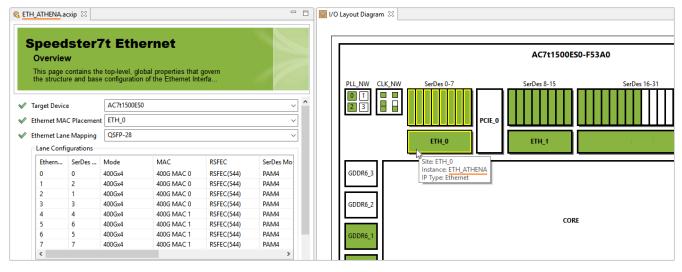

| I/O Designer Toolkit Views      |    |

| I/O Designer Toolkit Views      | 63 |

| I/O Ring Design File Generation | 63 |

| I/O Utilization View            |    |

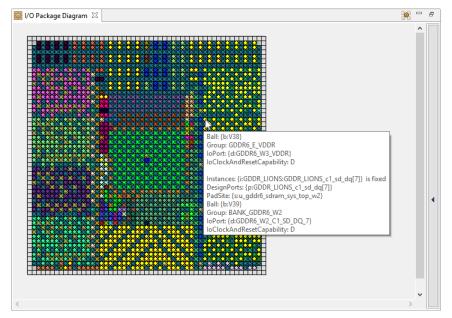

| I/O Package Diagram View        | 65 |

| I/O Pin Assignment View         |    |

| I/O Core Pin Assignment View    |    |

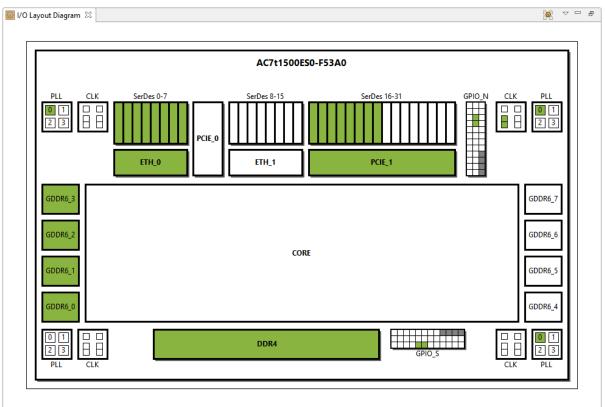

| I/O Layout Diagram View         |    |

| IP Diagram View                 | 71 |

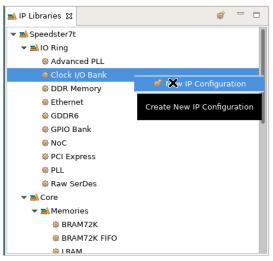

| IP Libraries View               | 73 |

| IP Problems View                |    |

| Multiprocess View               |    |

| Execution Queue Management      |    |

| Multiprocess Flow Management    |    |

| Select Implementations          |    |

| Multiprocess Run Logs           |    |

| Netlist Browser View            |    |

| Filtering Displayed Instances   |    |

| Drag-and-Drop                   |    |

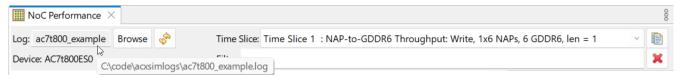

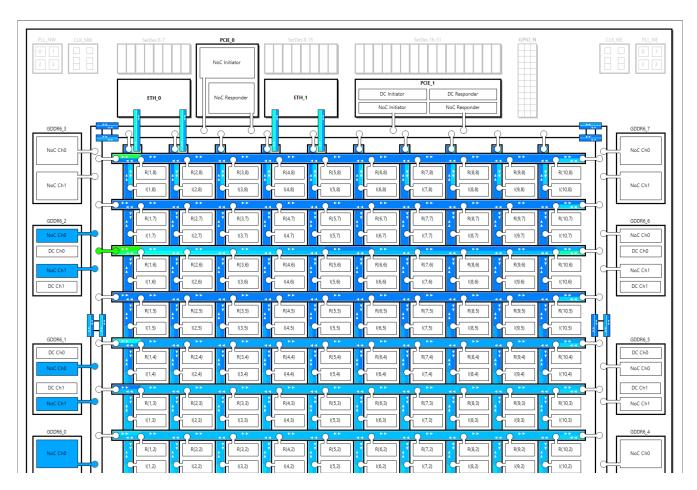

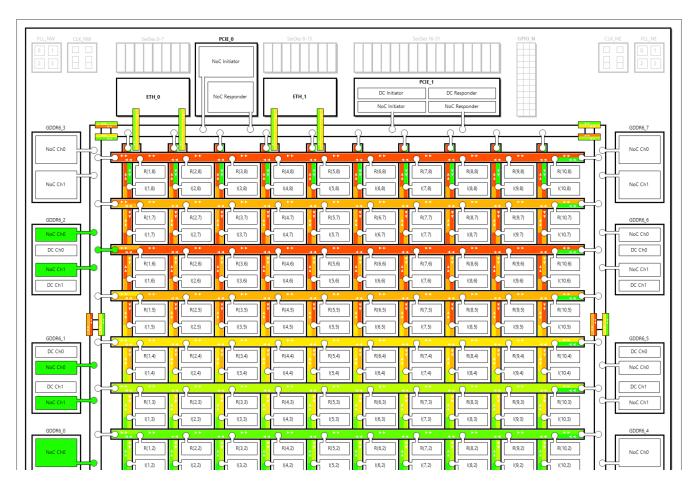

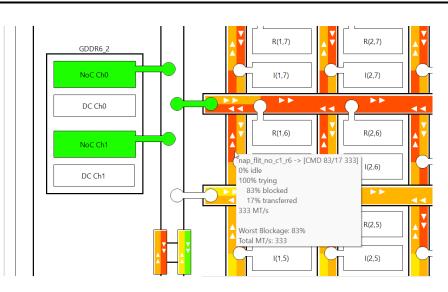

| NoC Performance View            |    |

| Loading Simulation Log Files    |    |

| Browsing Time Slices            |    |

| NoC Time Slice View             |    |

| Adjusting View Properties       |    |

|     | Options View                                                          |     |

|-----|-----------------------------------------------------------------------|-----|

|     | Outline View                                                          |     |

|     | Partitions View                                                       | 111 |

|     | Drag-and-Drop                                                         |     |

|     | Partial Reconfig Cluster Value                                        |     |

|     | Placement Regions View                                                |     |

|     | Using the Table to Display Placement Regions in the Floorplanner View |     |

|     | Organizing Table Data                                                 |     |

|     | Partial Reconfig Cluster Value                                        |     |

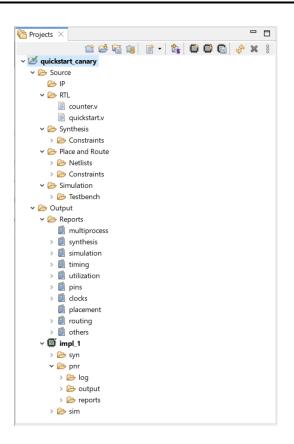

|     | Projects View                                                         |     |

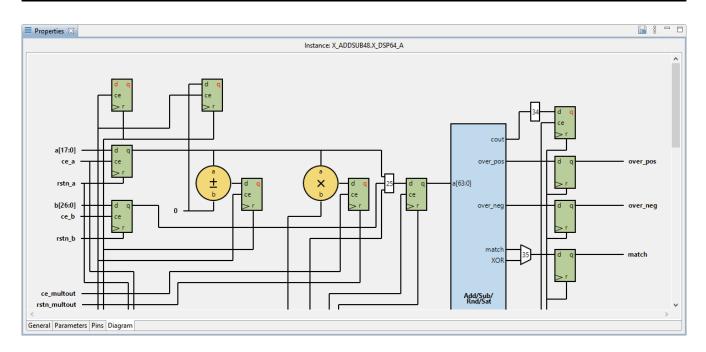

|     | Properties View                                                       |     |

|     | General Tab                                                           |     |

|     | Parameters Tab                                                        |     |

|     | Pins Tab                                                              |     |

|     | Diagram Tab                                                           |     |

|     | Save Properties                                                       |     |

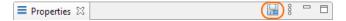

|     | Register Browser View                                                 |     |

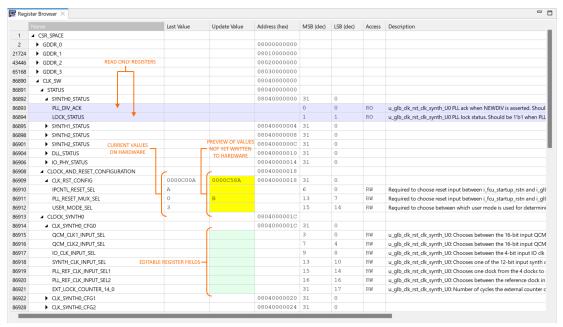

|     | Search View                                                           |     |

|     | Search Results and ACE Selection                                      |     |

|     | Search Highlights                                                     |     |

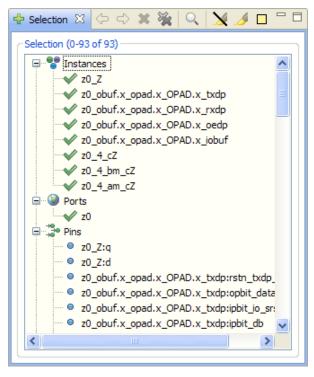

|     | Selection View                                                        |     |

|     | Snapshot Debugger View                                                | 141 |

|     | Tcl Console View                                                      |     |

| Dia | logs                                                                  | 150 |

|     | Add Signals to Waveform Viewer Dialog                                 |     |

|     | Add Source Files Dialogs                                              |     |

|     | Add IP Configuration Files Dialog                                     |     |

|     |                                                                       |     |

| Add RTL Files Dialog                        |     |

|---------------------------------------------|-----|

| Add Synthesis Constraint Files Dialog       |     |

| Add Place and Route Constraint Files Dialog |     |

| Add Place and Route Netlist Files Dialog    |     |

| Add Simulation Testbench Files Dialog       |     |

| Assign Bussed Signal Names Dialog           | 155 |

| Assign Bussed Values Dialog                 | 157 |

| Method 1                                    |     |

| Method 2                                    |     |

| Configure Clock Pre-Routes Dialog           | 159 |

| Create a New Constraints File Dialog        |     |

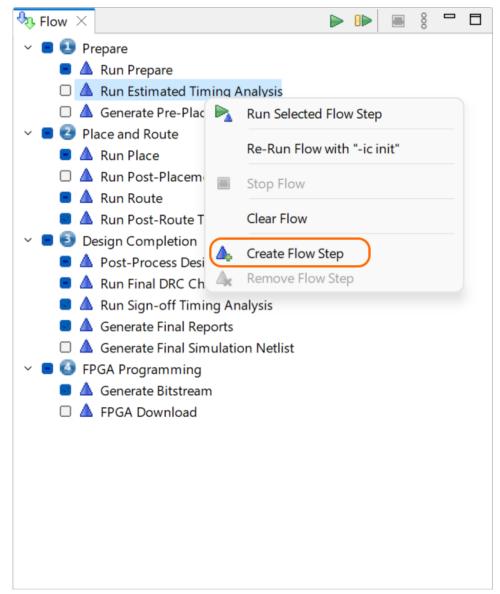

| Create a New Flow Step dialog               |     |

| Create a New Text File Dialog               |     |

| Create a SecureShare Zip File Dialog        |     |

| Configuration                               |     |

| ACE Input Files                             |     |

| ACE Output Files                            |     |

| Create Implementation Dialog                | 170 |

| Create Placement Region Dialog              |     |

| Create Project Dialog                       | 174 |

| Generate I/O Ring Design Files Dialog       | 175 |

| Generate IP Design Files Dialog             |     |

| Load Acxdb Dialog                           |     |

| Load Project Dialog                         |     |

| New IP Configuration Dialog                 |     |

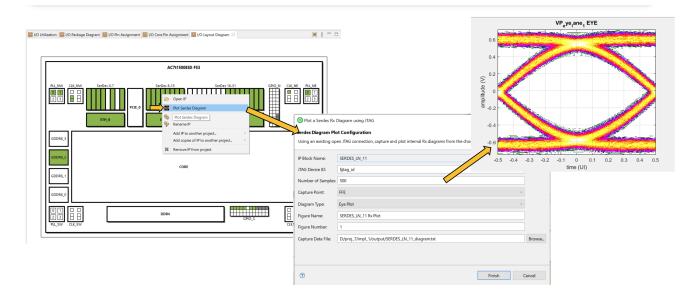

| Plot SerDes Diagram Dialog                  |     |

| MATLAB SerDes Eye Plot Y-axis Unit Formula  |     |

| Restore Implementation Dialog                                      |     |

|--------------------------------------------------------------------|-----|

| Save Implementation Dialog                                         |     |

| Save Placement Dialog                                              |     |

| Save Placement Regions Dialog                                      |     |

| Search Filter Builder Dialog                                       |     |

| Toolbars                                                           |     |

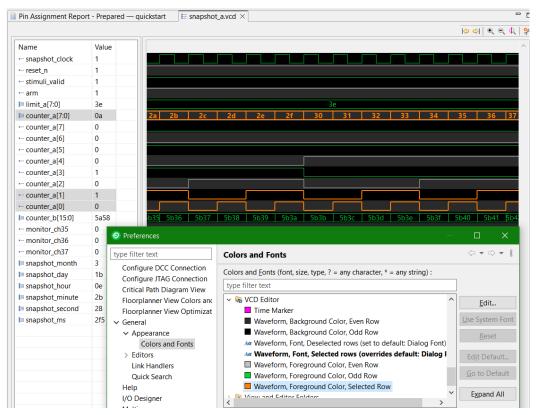

| Preferences                                                        |     |

| Configure DCC Connection Preference Page                           |     |

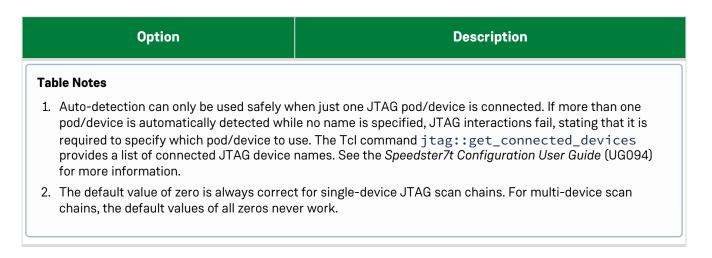

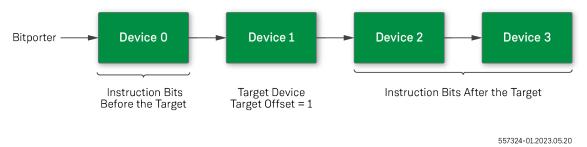

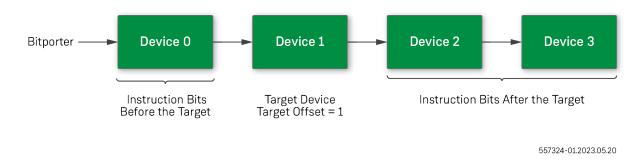

| Configure JTAG Connection Preference Page                          |     |

| Multi-device JTAG Scan Chain (IEEE 1149.1) Example                 |     |

| Critical Path Diagram View Preference Page                         |     |

| Cross Probe Preference Page                                        |     |

| Floorplanner View Colors and Layers Preference Page                |     |

| Floorplanner View Optimizations Preference Page                    | 203 |

| I/O Designer Preference Page                                       | 207 |

| IP Diagram Color and Font Preferences Section                      |     |

| Multiprocess: Configure Custom Job Submission Tool Preference Page |     |

| Netlist Browser Preference Page                                    |     |

| NoC Performance View Preference Page                               | 212 |

| Other Colors and Fonts Preference Page                             |     |

| Placement Regions Preference Page                                  |     |

| Project Management Preference Page                                 | 217 |

| Tcl Console View Preference Page                                   |     |

| Text Editors Preference Page                                       |     |

| Quick Diff Preference Page                                         | 223 |

| Projects                                                           | 224 |

| Project File                       | 224 |

|------------------------------------|-----|

| Source Files                       | 226 |

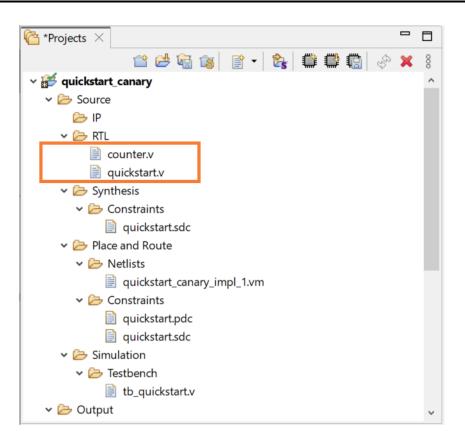

| RTL Files                          | 228 |

| Synthesis Constraints Files        | 228 |

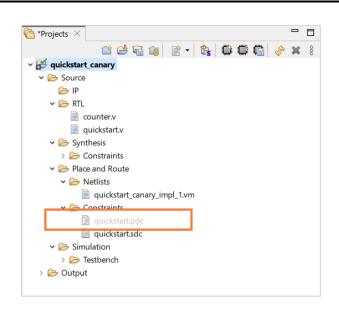

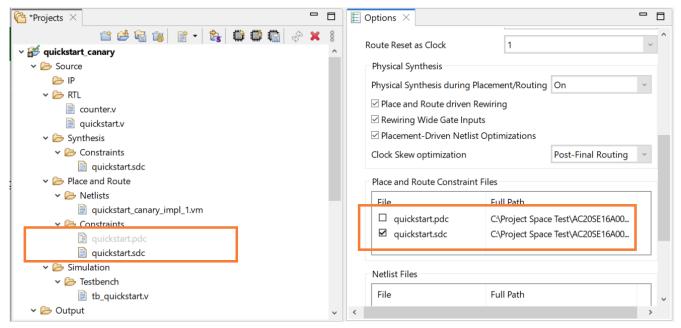

| Place and Route Constraints Files  | 228 |

| Place and Route Netlist Files      | 229 |

| Simulation Testbench Files         |     |

| Port Mapping Files                 |     |

| Implementations                    | 231 |

| Active Project and Implementation  | 231 |

| Project and Implementation Options | 231 |

| Project Options                    | 232 |

| Implementation Options             | 232 |

| Option Sets                        | 232 |

| Output Files                       | 233 |

| Log Files                          | 233 |

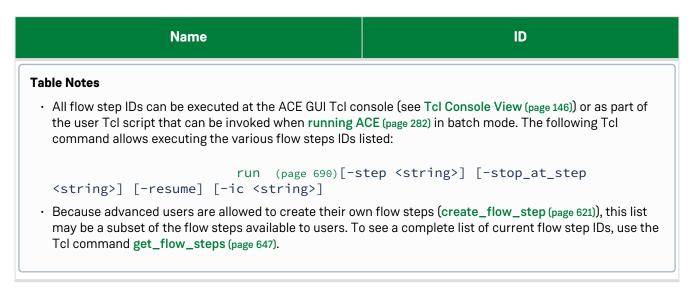

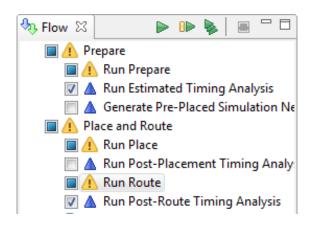

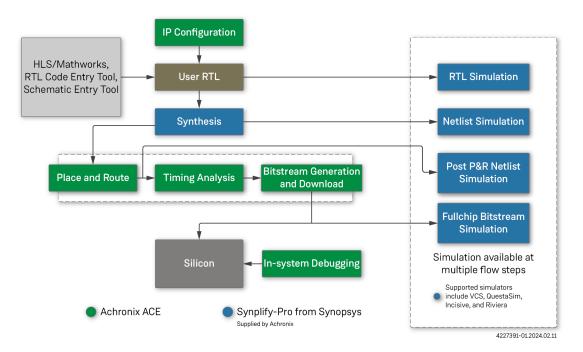

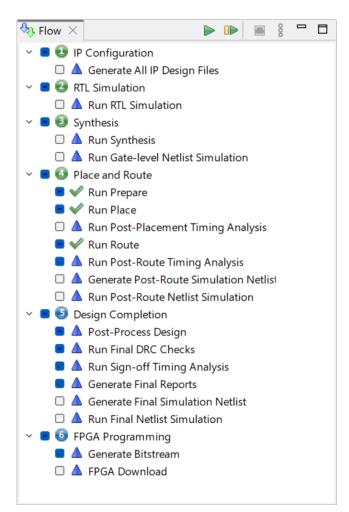

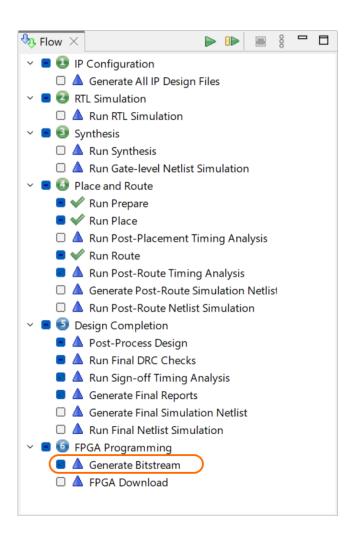

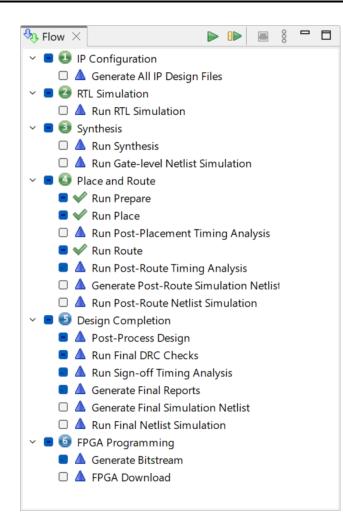

| Flow                               | 235 |

| Flow Steps                         | 235 |

| IP Configuration Steps             |     |

| RTL Simulation Steps               |     |

| Synthesis Steps                    |     |

| Place and Route Steps              |     |

| Design Completion Steps            | 241 |

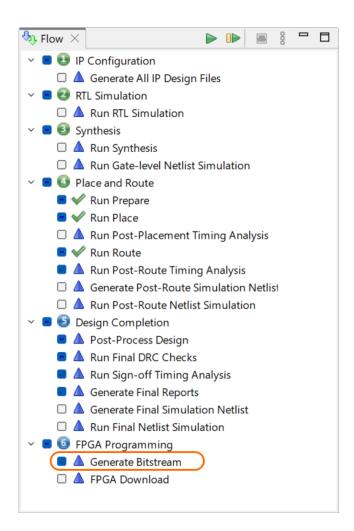

| FPGA Programming Steps             | 242 |

| Flow Status                        | 243 |

| Flow Mode                          | 243 |

| Reports                                                      |     |

|--------------------------------------------------------------|-----|

| Utilization Report                                           | 244 |

| Pin Assignment Report                                        | 245 |

| Clock Report                                                 | 245 |

| Timing Report                                                | 245 |

| Report Content                                               |     |

| Routing Report                                               | 246 |

| Partitions Report                                            | 246 |

| Power Dissipation Report                                     | 246 |

| Example Power Dissipation Report                             |     |

| Power Calculation Methodology                                |     |

| How to Generate the Power Dissipation Report                 |     |

| How to Generate a Simulation-Driven Power Dissipation Report |     |

| Design Statistics Report                                     | 256 |

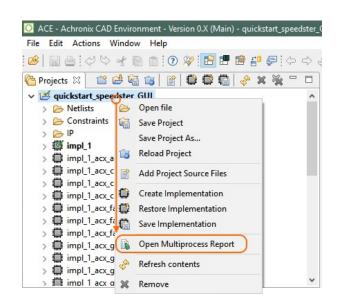

| Multiprocess Summary Report                                  | 256 |

| Timing Results Summary Section                               | 257 |

| Runtime Results Summary Section                              |     |

| Implementation Options Report                                | 258 |

| Advanced Concepts                                            |     |

| ACE Verilog Attributes                                       | 259 |

| locked                                                       |     |

| fanout_limit                                                 |     |

| must_keep                                                    |     |

| do_not_rewire                                                |     |

| do_not_clone                                                 |     |

|                                                              |     |

| clock_type                                       | .260  |

|--------------------------------------------------|-------|

| local_clock_type                                 | 261   |

| ace_useioff                                      | 261   |

| ace_virtualize                                   | 261   |

| ace_virtualize_clock_port                        | 261   |

| ace_virtualize_clock_net                         | 261   |

| async_capture                                    | . 262 |

| location                                         | . 262 |

| Clock Regions                                    | .262  |

| Instance States                                  | .262  |

| Filter Properties                                | .264  |

| Timing Across All Temperature Corners            | 266   |

| Temperature Corners and Place and Route          | .266  |

| Temperature Corners and Timing Analysis/Reports: | 267   |

| ECO Commands                                     | 268   |

| ECO Use Cases                                    | .268  |

| Net Legality Definition                          | .268  |

| Disclaimers                                      | .268  |

| ECO Commands                                     | .269  |

| GUI Support                                      | 275   |

| Add Instance Pin Dialog                          | 276   |

| ECO Insert Instance Dialog                       | 276   |

| ECO Insert Net Dialog                            | 278   |

| ECO Rewire Instance Dialog                       | 279   |

| ECO Rewire Net Dialog                            | .280  |

| Fabric Clusters                                  | . 281 |

| U | G   | 07  | 70 |

|---|-----|-----|----|

| ~ | ~ ` | ~ ^ | ~  |

| Chapter 4 : Tasks                                       | 282 |

|---------------------------------------------------------|-----|

| Running ACE                                             | 282 |

| GUI Mode                                                |     |

| Command-line Mode                                       |     |

| Batch Mode                                              | 283 |

| Lab Mode (Reduced Functionality)                        |     |

| ACE Initialization Script (ACE_INIT_SCRIPT)             |     |

| Relative paths                                          |     |

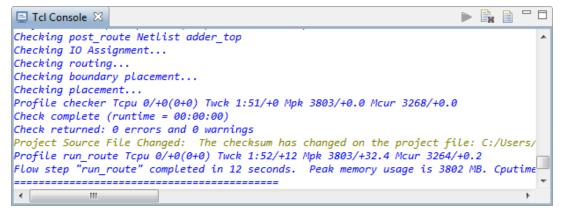

| Example Log Output                                      |     |

| ACE Startup Arguments                                   | 285 |

| Working With Perspectives                               | 286 |

| Switching Between Perspectives                          |     |

| Resetting Perspectives                                  |     |

| Working with Views and Editors                          | 287 |

| Opening Views                                           |     |

| Moving and Docking Views and Editors                    |     |

| Rearranging Tabbed Views and Editors                    |     |

| Detaching Views and Editors                             |     |

| Tiling Editors                                          | 289 |

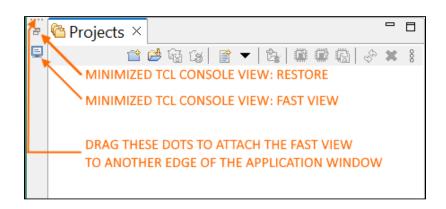

| Maximizing, Minimizing, and Restoring Views and Editors |     |

| Maximize:                                               |     |

| Minimize:                                               |     |

| Working with Projects and Implementations               | 293 |

| Creating Projects                                       | 293 |

| Saving Projects                                         | 293 |

| Loading Projects                                                     | 294                                                                                              |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Loading a Project Using the GUI                                      |                                                                                                  |

| Loading a Project Using Tcl                                          |                                                                                                  |

| Project Locking and Lock Files                                       |                                                                                                  |

| Removing Projects                                                    | 296                                                                                              |

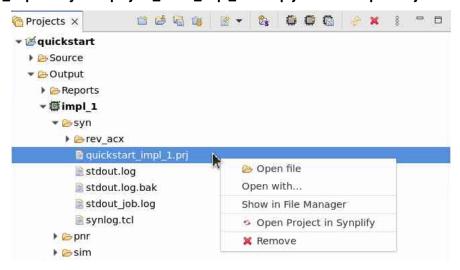

| Opening Project Files in an Editor                                   | 296                                                                                              |

| Adding Source Files                                                  | 296                                                                                              |

| Source File Load Order                                               |                                                                                                  |

| Enabling/Disabling Netlists and Constraint Files for Implementations |                                                                                                  |

| Removing Source Files                                                |                                                                                                  |

| Disabling Constraint Files                                           |                                                                                                  |

| Opening Source Files in an Editor                                    |                                                                                                  |

| Creating Implementations                                             |                                                                                                  |

| Saving Implementations                                               |                                                                                                  |

| Restoring Implementations                                            |                                                                                                  |

| Copying Implementations                                              |                                                                                                  |

| Setting the Active Implementation                                    |                                                                                                  |

| Removing Implementations                                             |                                                                                                  |

| Configuring Project and Implementation Options                       | 303                                                                                              |

| Opening Output Files in an Editor                                    | 303                                                                                              |

| Opening Report Files in an Editor                                    | 303                                                                                              |

| Cleaning Projects                                                    | 303                                                                                              |

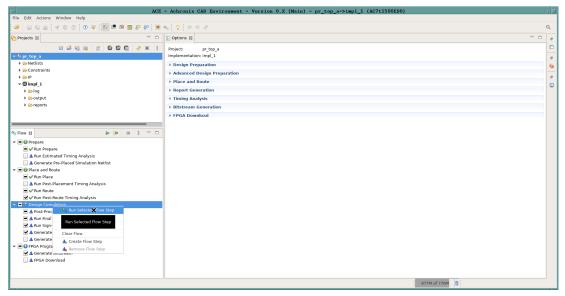

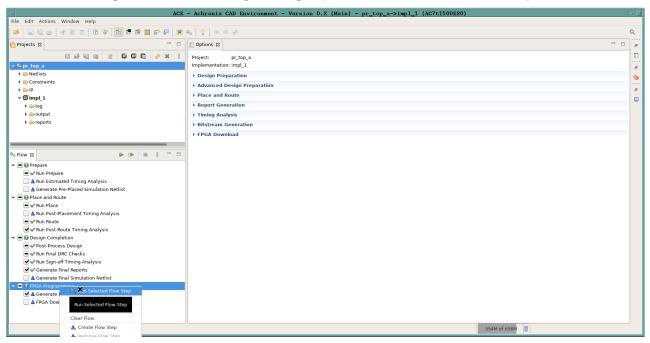

| nning the Flow                                                       |                                                                                                  |

| Running the Entire Flow                                              | 305                                                                                              |

| Running a Sub-Flow                                                   |                                                                                                  |

| Run an Individual Flow Step                                          |                                                                                                  |

|                                                                      | Loading a Project Using the GUI<br>Loading a Project Using Tcl<br>Project Locking and Lock Files |

| 1 | 10 | $\sim$ | - | $\sim$ |

|---|----|--------|---|--------|

| L | JG | U      | / | U      |

| Run Remaining Enabled Flow Steps (Resume Flow)                              |     |

|-----------------------------------------------------------------------------|-----|

| Stopping the Flow                                                           | 307 |

| Running Multiple Flows in Parallel                                          |     |

| Finding the Multiprocess View                                               | 307 |

| Configuring the Execution Queues                                            | 307 |

| Configuring the Desired Flow to be Followed by the Selected Implementations |     |

| Selecting the Implementations to be Run in Parallel                         |     |

| Starting Background Execution                                               |     |

| Stopping/Canceling Background Execution                                     |     |

| Viewing the Results                                                         |     |

| Multiprocess Batch Mode                                                     | 317 |

| Detecting Changes to Project Source Files                                   |     |

| Files Open in the ACE Editor Area                                           | 323 |

| Smart Change Detection Using Custom Checksums                               | 323 |

| Saving the Active Implementation                                            | 323 |

| Restoring the Active Implementation                                         | 323 |

| Caching the Project Source File State                                       | 324 |

| Automatic Checking while Running the Flow                                   | 324 |

| Warning Visualization in the Flow View                                      | 324 |

| Pop-up Dialog Warnings                                                      | 325 |

| Managing Pop-up Preferences                                                 | 326 |

| Tcl Command Support                                                         | 329 |

| Custom Flow Steps                                                           |     |

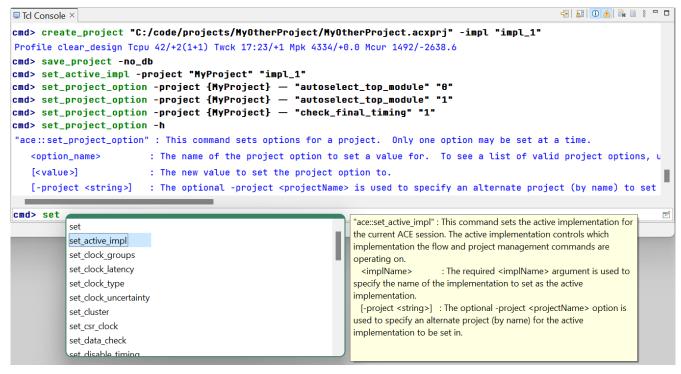

| Using the Tcl Console                                                       | 331 |

| Sending Commands from GUI Actions                                           |     |

| Sending Commands from the Console                                           |     |

| Command Highlighting                                                        | 331 |

| С     | ommand Auto-Completion                                | 331 |

|-------|-------------------------------------------------------|-----|

| С     | ommand Help                                           |     |

| Te    | ext Limit                                             |     |

| CI    | learing the Console                                   | 334 |

| Vi    | iewing the ACE Log File                               | 334 |

| 01    | bject Type Prefixes                                   | 334 |

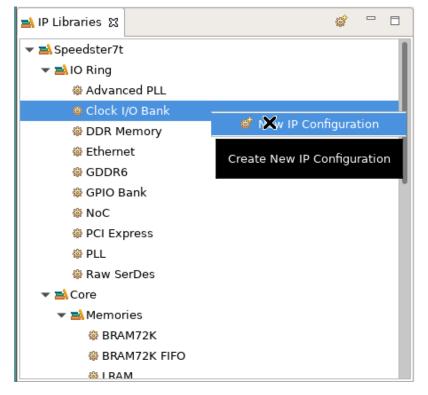

| Creat | ing an IP Configuration                               | 335 |

| Сі    | reating and Naming an IP Configuration                | 336 |

| Se    | etting the IP Configuration                           | 336 |

|       | Editable Fields                                       |     |

|       | Calculated Fields                                     |     |

|       | IP Editor Navigation                                  |     |

| G     | enerating the IP Design Files                         | 338 |

| A     | dding Configuration Files to a Project                | 338 |

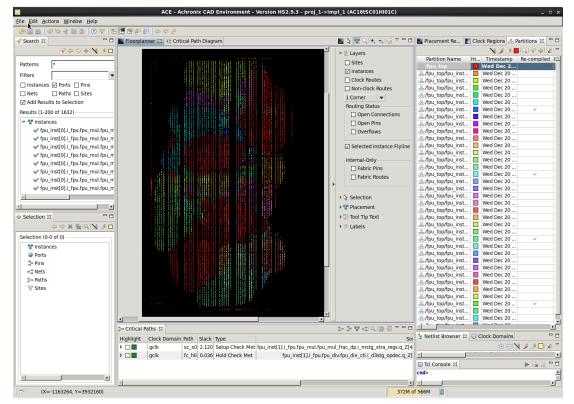

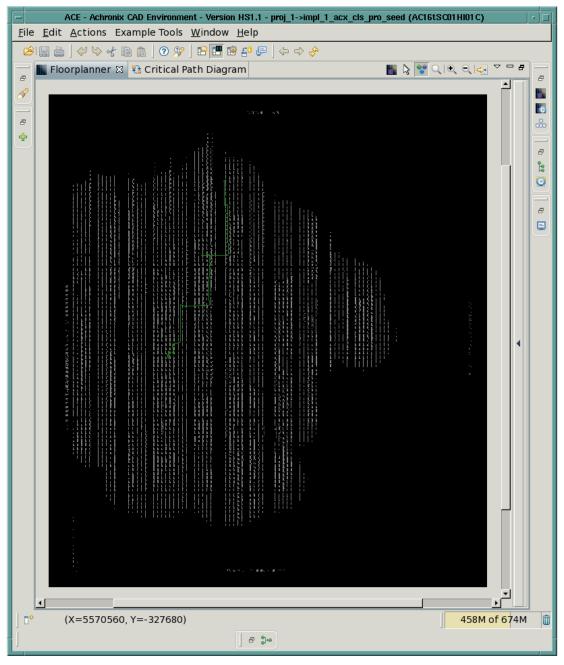

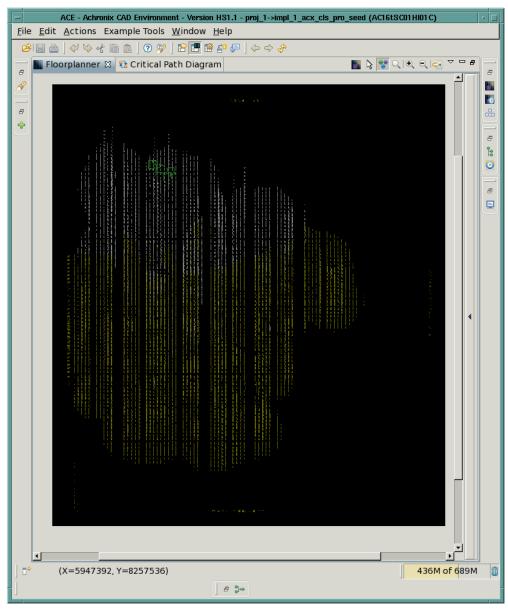

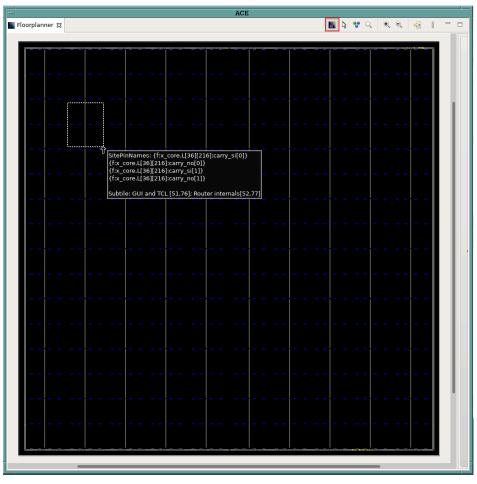

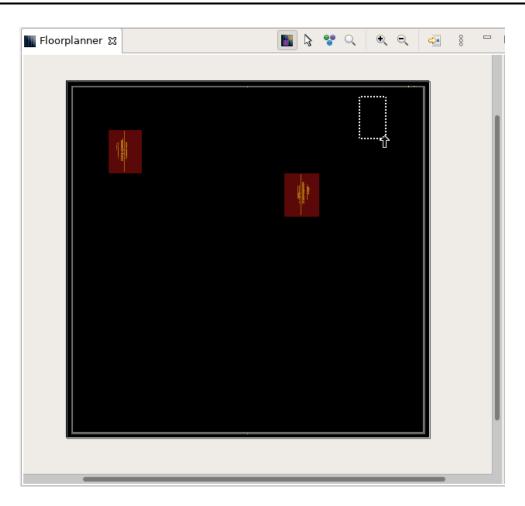

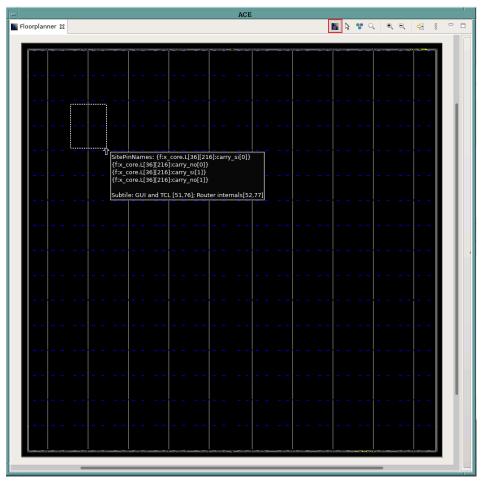

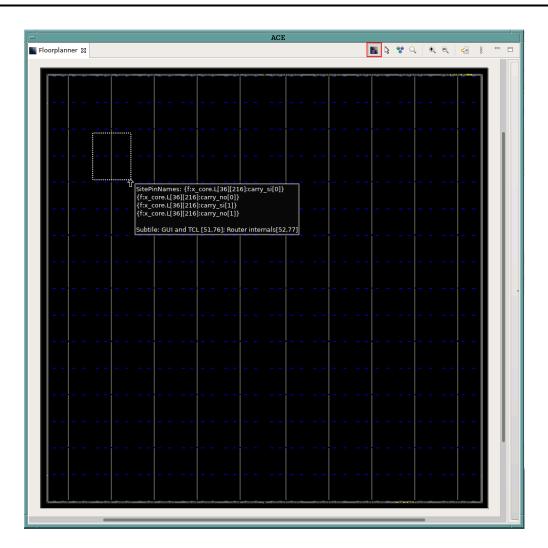

| Viewi | ing the Floorplanner                                  | 338 |

| O     | pening and Closing the Floorplanner's Fly-Out Palette | 338 |

| Zo    | ooming the Floorplanner In and Out                    | 338 |

| FI    | loorplanner Panning                                   | 339 |

| Se    | electing Floorplanner Objects                         | 340 |

| De    | eselecting Floorplanner Objects                       | 340 |

| То    | oggling Floorplanner Mouse Tools                      |     |

| Fi    | iltering the Floorplanner View                        | 341 |

|       | Filtering with Layers                                 |     |

|       | Filtering with Selection                              |     |

| CI    | hoosing Floorplanner Object Tooltips                  |     |

| Vi    | iewing Floorplanner Object Labels                     | 342 |

| UG070 |  |

|-------|--|

|       |  |

| Highlighting Objects in the Floorplanner View                     | 342 |

|-------------------------------------------------------------------|-----|

| Selection vs. Highlighting                                        |     |

| Objects May Be Both Selected and Highlighted Simultaneously       |     |

| Batch Mode Highlighting                                           |     |

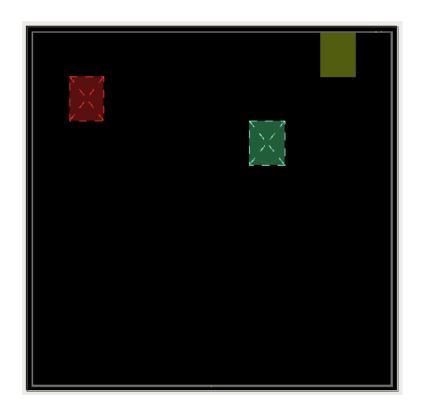

| Pre-Placing a Design                                              |     |

| Placing an Object                                                 | 346 |

| Changing Between Fixed and Soft Placement                         |     |

| Fixing placement of soft-placement objects                        |     |

| Un-fixing (softening) placement of fixed-placement objects        |     |

| Group Placement Mode                                              |     |

| Adjusting the Existing Placement of a Group of Selected Instances |     |

| Removing Placement                                                | 350 |

| Saving Pre-Placement Constraints                                  | 350 |

| Using Pre-Placement in the Flow                                   |     |

| Types of Pre-Placement                                            |     |

| Recommended Typical Flow                                          |     |

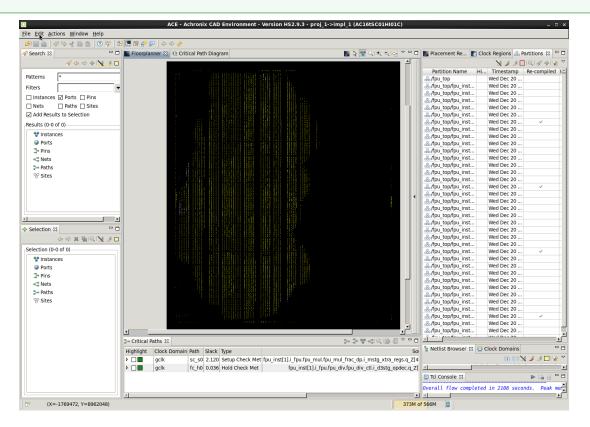

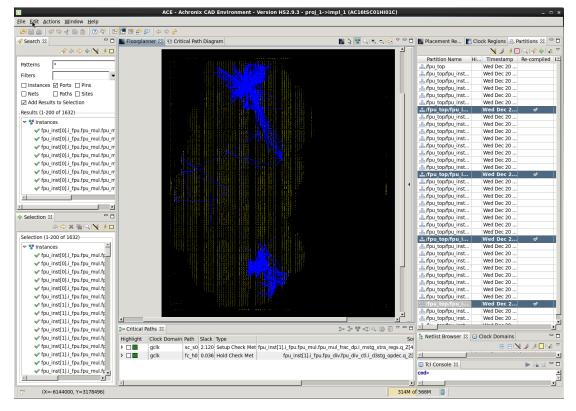

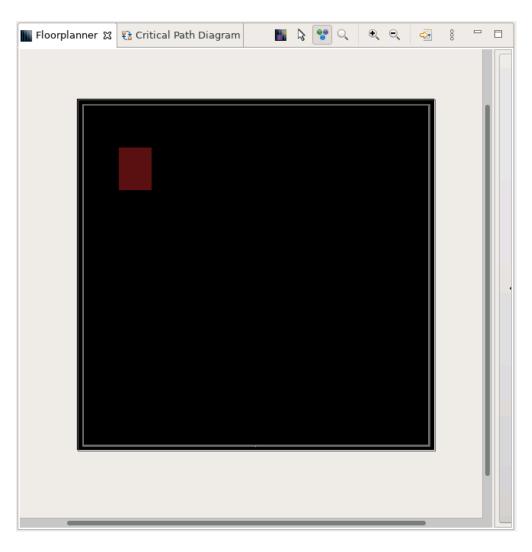

| Analyzing Critical Paths                                          |     |

| Generating Timing Reports                                         | 352 |

| Highlighting Critical Paths                                       | 353 |

| Selecting Critical Path Objects                                   | 353 |

| Zooming to Critical Paths                                         | 354 |

| Printing Critical Path Details                                    | 354 |

| Using Critical Path Diagrams                                      | 355 |

| Graph Elements                                                    |     |

| Critical Path Diagram Types                                       |     |

| Adding Portions of the Graph to the ACE Selection Set             |     |

| Applying and Checking Properties             | 356 |

|----------------------------------------------|-----|

| Applying Properties                          |     |

| defparam                                     |     |

| RTL Attribute                                |     |

| set_property Tcl Command                     |     |

| Checking Whether Properties Were Applied     |     |

| Configuring External Connections to Hardware | 357 |

| Configuring the DCC Connection               |     |

| Background Info                              |     |

| Installing DCC USB Drivers                   |     |

| Configuring the USB drivers                  |     |

| Configuring ACE                              |     |

| Configuring the JTAG Connection              |     |

| JTAG Programmer Device Connection            |     |

| JTAG Scan Chain                              |     |

| Running the Snapshot Debugger                |     |

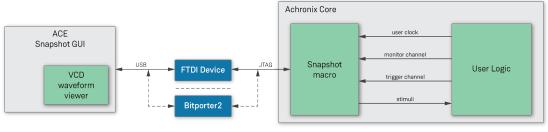

| Snapshot Design Flow                         |     |

| Accessing the Snapshot Debugger              |     |

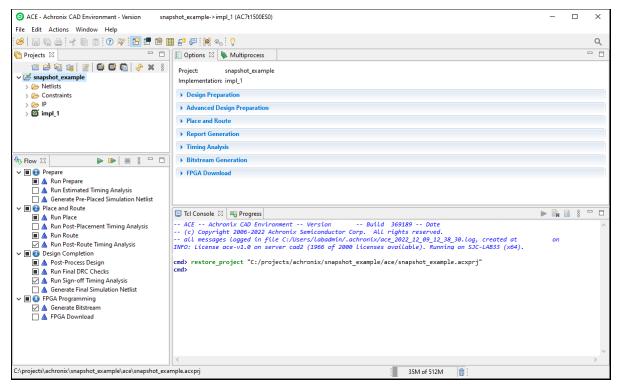

| Open the ACE GUI and Select the Project      |     |

| Open the Snapshot Debugger                   |     |

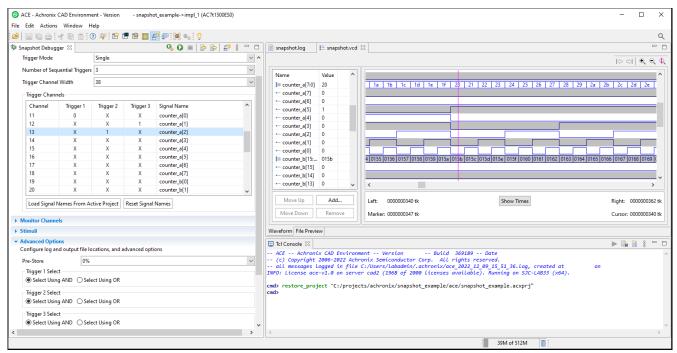

| Configuring the Trigger Pattern              |     |

| Configuring the Trigger Mode                 |     |

| Configuring Trigger Patterns                 |     |

| Configuring the Monitor Signals              |     |

| Naming Captured Signal Data                  |     |

| Configuring Test Stimulus                    |     |

| UG070 |

|-------|

| 000/0 |

| Setting Stimuli Values Using the Table                                  |  |

|-------------------------------------------------------------------------|--|

| Setting Multiple Stimuli Values as a Bus                                |  |

| Configuring Advanced Options                                            |  |

| Pre-Store                                                               |  |

| Trigger Pattern Match Behavior                                          |  |

| User Clock Frequency                                                    |  |

| Configure Output File Locations                                         |  |

| Collecting Samples of the User Design                                   |  |

| Arming the Snapshot Debugger                                            |  |

| Using the Startup Trigger                                               |  |

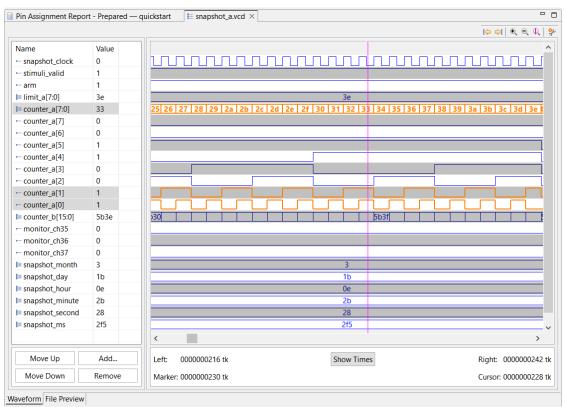

| Viewing the Captured VCD Waveform                                       |  |

| Opening a VCD file                                                      |  |

| Viewing the Raw Text Content                                            |  |

| Viewing the Signal Data as Waveforms                                    |  |

| Saving/Loading Snapshot Configurations                                  |  |

| Snapshot in Batch Mode                                                  |  |

| Programming a Device using JTAG in the Download View                    |  |

| Selecting a Bitstream File                                              |  |

| Lab Mode                                                                |  |

| Selecting Bitstream Programming Options                                 |  |

| Downloading the Bitstream to the Target Device                          |  |

| Optimizing a Design                                                     |  |

| Attempting Likely Optimizations Using Option Sets                       |  |

| Selecting the Implementations to be Generated and Run in Parallel       |  |

| Generating Option Set Implementations and Starting Background Execution |  |

| Interpreting/Utilizing the Results                                      |  |

|                                                                         |  |

| LIG070 |  |

|--------|--|

| 000/0  |  |

| Placement Regions and Placement Region Constraints                   |     |

|----------------------------------------------------------------------|-----|

| Placement Region Preferences                                         |     |

| Creating a New Placement Region                                      |     |

| Resizing an Existing Placement Region                                |     |

| Moving an Existing Placement Region                                  |     |

| Assigning Placement Region Constraints                               |     |

| Listing all Objects Constrained to a Placement Region                |     |

| Removing a Placement Region Constraint from an Object                |     |

| Saving Placement Region Definitions and Placement Region Constraints |     |

| Deleting Placement Regions                                           |     |

| Running the HW Demo                                                  | 401 |

| Installing HW Demo Designs                                           |     |

| HW Demo Installation Paths                                           |     |

| Selecting The Target Device And Demo                                 | 402 |

| Loading The Demo JAM File                                            | 402 |

| Displaying Board Status                                              | 403 |

| Control of Running Demonstration Design                              | 403 |

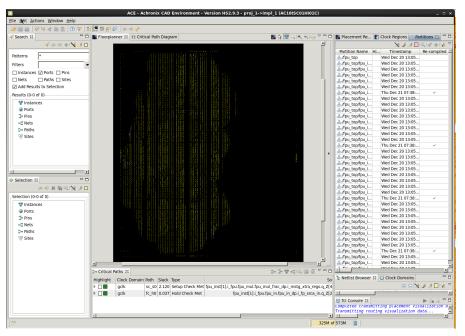

| Using Incremental Compilation (Partitions)                           | 404 |

| Overview of Incremental Compilation and Partitions                   |     |

| Defining Partitions                                                  |     |

| Enabling Incremental Compilation                                     |     |

| Tracking Partition Status                                            |     |

| Forcing an Unchanged Partition to Recompile                          |     |

| Viewing Instances In Partitions                                      |     |

| Related Tcl Commands                                                 |     |

| Incremental Compile Tutorial                                         | 407 |

| Overview                                                            | 407 |

|---------------------------------------------------------------------|-----|

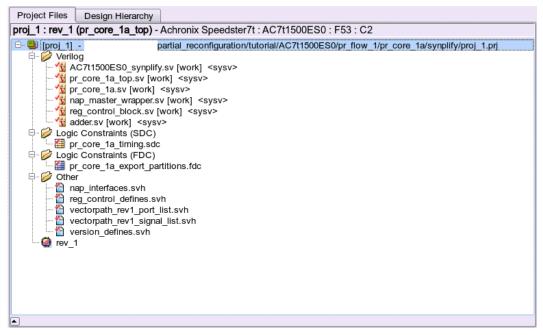

| Tutorial Files                                                      | 407 |

| Single-Process Incremental Compile Tutorial                         | 408 |

| Step 1: Obtaining the Files                                         | 409 |

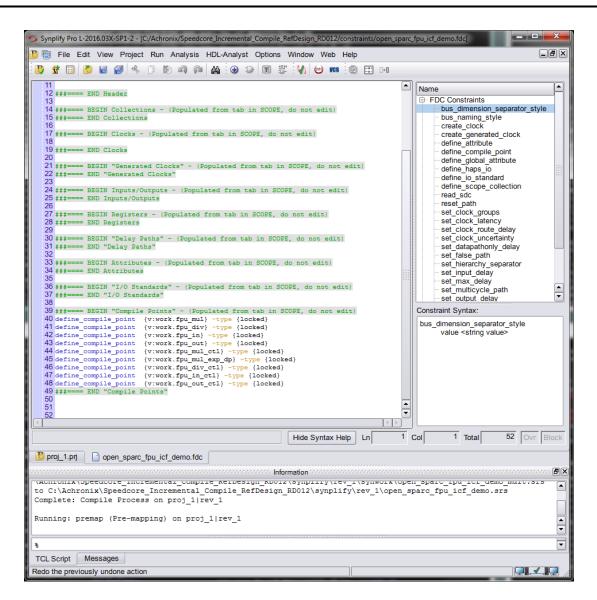

| Step 2: Set up the Synthesis Project                                | 409 |

| Step 3: Compile the Design in Synplify Pro                          | 414 |

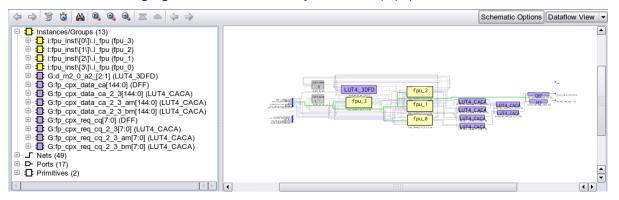

| Step 4: Review Synplify Results                                     | 417 |

| Step 5: Set up the ACE Project                                      | 421 |

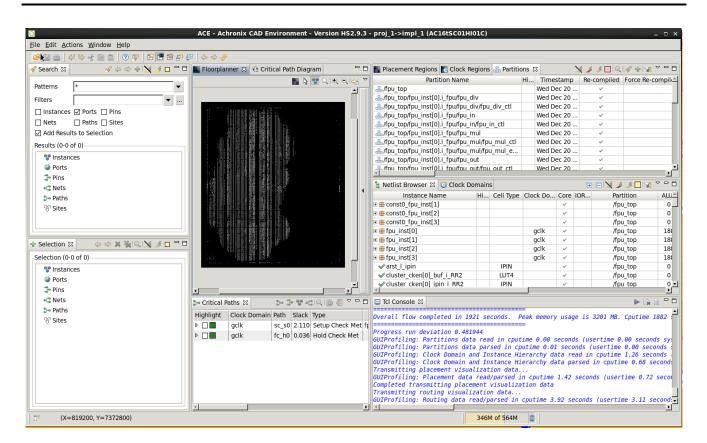

| Step 6: Compile the Design in ACE                                   | 424 |

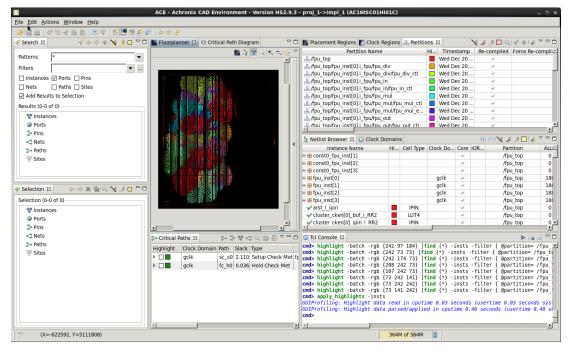

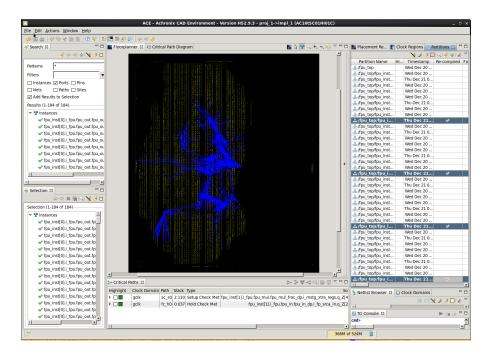

| Step 7: Review ACE Results                                          | 424 |

| Step 8: Change the RTL (rtl_V1)                                     | 430 |

| Step 9: Recompile the Design in Synplify Pro (rtl_V1)               | 430 |

| Step 10: Review Synplify Results (rtl_V1)                           | 430 |

| Step 11: Recompile the Design in ACE (rtl_V1)                       | 432 |

| Step 12: Review ACE Results (rtl_V1)                                | 433 |

| Step 13: Additional Incremental Iterations                          | 436 |

| Step 14: Review ACE Results (rtl_V2)                                | 437 |

| Step 15: Review ACE Results (rtl_V3)                                | 439 |

| Step 16: Review ACE Results (rtl_V4)                                | 441 |

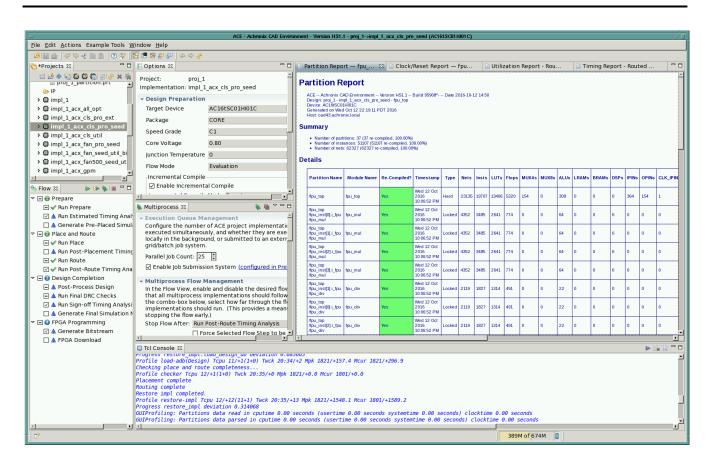

| Multiprocess Incremental Compile Tutorial                           | 443 |

| Step 1: Compile the Design in Synplify Pro or Clear the ACE Project | 443 |

| Step 2: Create Multiprocess Implementations and Run ACE             | 443 |

| Step 3: Select the Implementation with Best Performance             | 445 |

| Step 4: Change the RTL and Recompile the Design in Synplify Pro     | 448 |

| Step 5: Recompile the Multiprocess Implementations in ACE           | 448 |

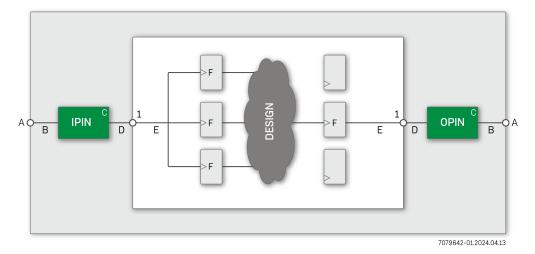

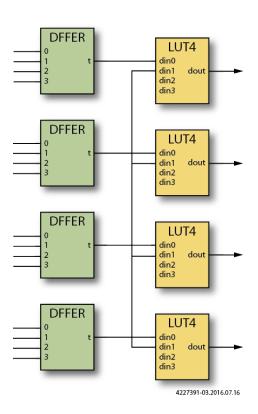

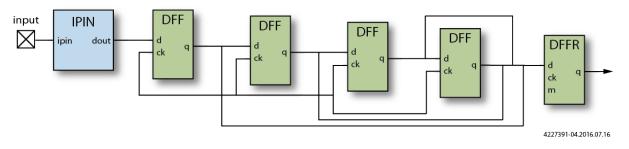

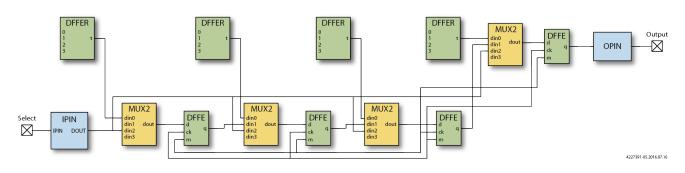

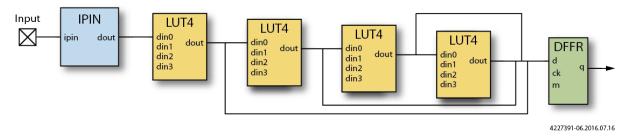

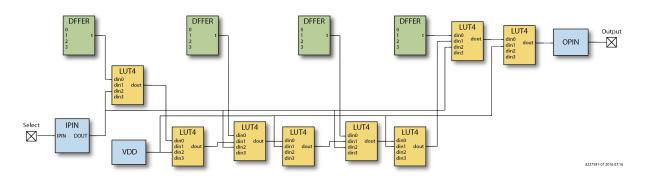

| Automatic Flop Pushing into I/O Pins                                | 452 |

| Background                                                          | 452 |

| Capabilities                                                | 453 |

|-------------------------------------------------------------|-----|

| ACE Implementation Options                                  |     |

| push_flops_into_pads                                        |     |

| pad_flop_pushing_clock_type                                 |     |

| ACE Attributes                                              | 455 |

| Examples                                                    | 456 |

| Timing Analysis Implications                                |     |

| Working with Virtual I/O                                    | 460 |

| Behavior                                                    |     |

| Implementation Options                                      |     |

| Port Attributes                                             |     |

| Runtime Messages                                            |     |

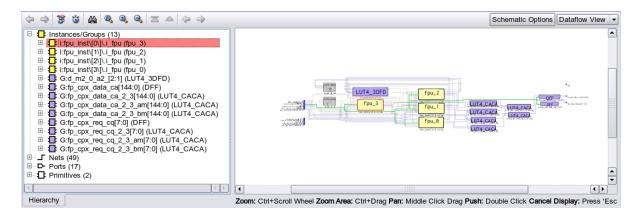

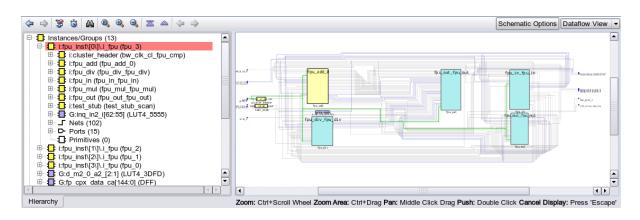

| Schematic View                                              |     |

| Input Netlist                                               |     |

| Output Netlist Styles                                       |     |

| Accessing Help                                              |     |

| Accessing Context-Sensitive Help                            |     |

| Navigating Help Topics                                      |     |

| Using the Help Window                                       |     |

| Using the Help View                                         |     |

| Searching Help                                              |     |

| Refining the Search Results                                 |     |

| Highlighting Search Terms                                   |     |

| Search Query Syntax                                         |     |

| Using the ACE SecureShare Tool to Create a Support Zip File | 471 |

| Importing and Exporting Preferences                         | 472 |

| Import Preferences                                                          |     |

|-----------------------------------------------------------------------------|-----|

| Export Preferences                                                          |     |

| Plotting SerDes Receiver Diagrams Using JTAG                                |     |

| Plotting a SerDes Diagram for a SerDes Lane                                 | 477 |

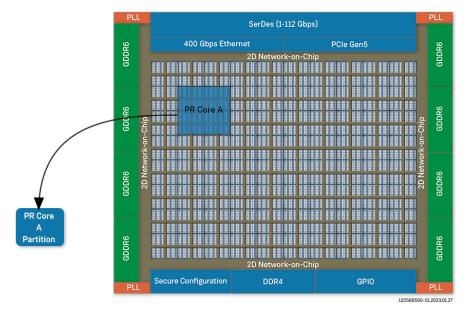

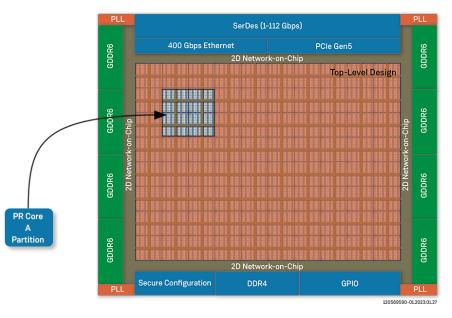

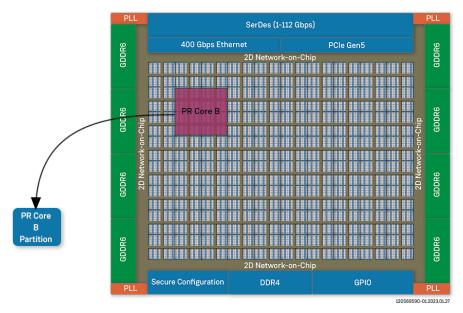

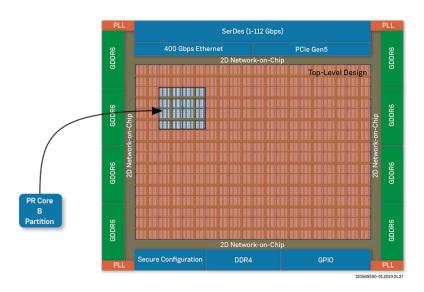

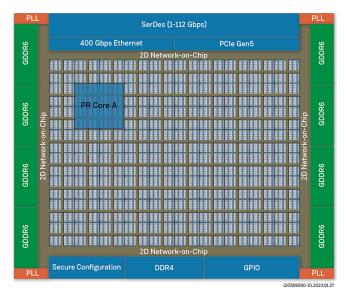

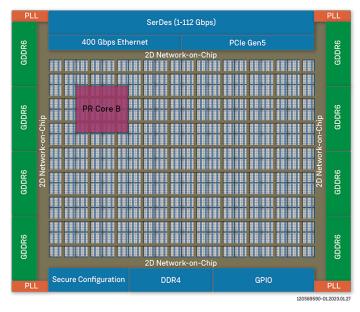

| Using Partial Reconfiguration                                               |     |

| Partial Reconfiguration Tutorial                                            | 479 |

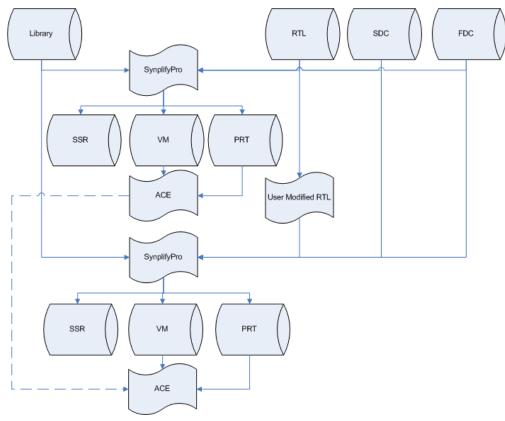

| Partial Reconfiguration Flows                                               |     |

| Flow Diagrams                                                               |     |

| Design Details                                                              |     |

| PR Flow 1: Multi-Project PR Flow Using Partition Export/Import              |     |

| PR Flow 2: Multi-Project PR Flow Using Keep Out Regions                     |     |

| Updating ROM, BRAM, or LRAM Memory Initialization Contents in the Bitstream |     |

| Initialized using a mem_init file                                           | 545 |

| Initialized using initd* parameters                                         |     |

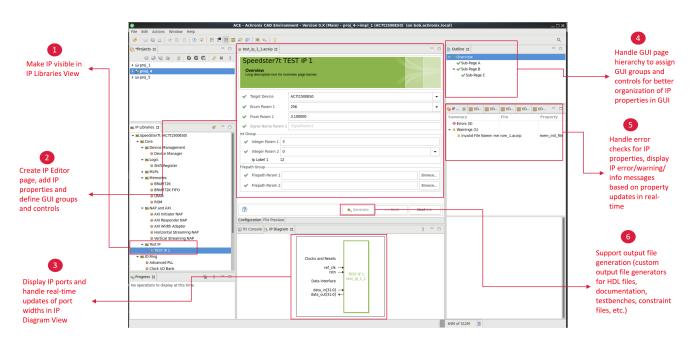

| Plugging in Custom IP Generator Tools                                       |     |

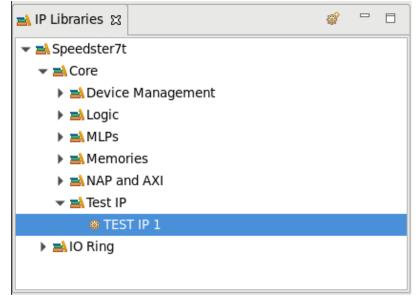

| File Location and Directory Organization                                    | 553 |

| Loading User-defined Directory Paths Using Environment Variables            |     |

| IP Generator Plugin Development                                             | 554 |

| Model Definition                                                            |     |

| View Definition                                                             |     |

| Control Definition                                                          |     |

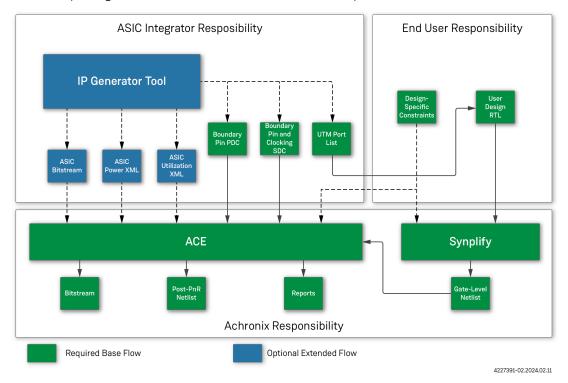

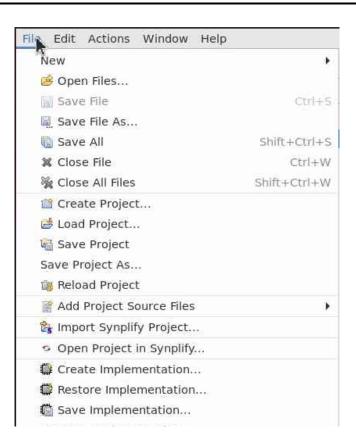

| Opening Synplify in ACE                                                     | 575 |

| ACE-Driven Integrated Synthesis                                             | 576 |

| Synplify-Pro-Driven Integrated Synthesis                                    |     |

| Opening Project from ACE File Menu                                          | 577 |

| Opening Project from ACE Actions Menu |  |

|---------------------------------------|--|

| Chapter 5 : Tcl Command Reference     |  |

| SDC Commands                          |  |

| all_clocks                            |  |

| Description                           |  |

| Example                               |  |

| Also See                              |  |

| all_inputs                            |  |

| Description                           |  |

| Example                               |  |

| Also See                              |  |

| all_outputs                           |  |

| Description                           |  |

| Example                               |  |

| Also See                              |  |

| create_clock                          |  |

| Description                           |  |

| Example                               |  |

| Also See                              |  |

| create_generated_clock                |  |

| Description                           |  |

| Example                               |  |

| Also See                              |  |

| get_cells                             |  |

| Description                           |  |

| Example                               |  |

|                                       |  |

|      | Also See           | 585 |

|------|--------------------|-----|

| get  | _clocks            | 586 |

|      | Description        |     |

|      | Example            |     |

|      | Also See           | 586 |

| get  | _nets              | 587 |

|      | Description        | 587 |

|      | Example            | 587 |

|      | Also See           | 587 |

| get  | _pins              | 587 |

|      | Description        |     |

|      | Example            |     |

|      | Also See           |     |

| get  | _ports             | 588 |

|      | Description        |     |

|      | Example            |     |

|      | Also See           |     |

| set. | _clock_groups      | 589 |

|      | Description        |     |

|      | Example            |     |

|      | Also See           |     |

| set. | _clock_latency     | 591 |

|      | Description        |     |

|      | Example            |     |

|      | Also See           | 592 |

| set. | _clock_uncertainty | 592 |

|      | Description        | 592 |

|      |                    |     |

| Example              |     |

|----------------------|-----|

| Also See             |     |

| set_data_check       |     |

| Description          |     |

| Example              |     |

| Also See             |     |

| set_disable_timing   |     |

| Description          |     |

| Example              |     |

| Also See             |     |

| set_false_path       |     |

| Description          |     |

| Example              |     |

| Also See             |     |

| set_input_delay      |     |

| Description          |     |

| Example              |     |

| Also See             |     |

| set_input_transition |     |

| set_load             |     |

| set_max_delay        |     |

| set_min_delay        |     |

| set_multicycle_path  |     |

| Description          | 601 |

| Example              |     |

| Also See             |     |

| set_output_delay     |     |

|                      |     |

| Description                                                                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Example                                                                                                                                                                                                |     |

| Also See                                                                                                                                                                                               |     |

| Interactive Timing Commands                                                                                                                                                                            | 603 |

| check_setup                                                                                                                                                                                            |     |

| Example                                                                                                                                                                                                |     |

| prepare_sta                                                                                                                                                                                            |     |

| Example                                                                                                                                                                                                |     |

| report_checks                                                                                                                                                                                          |     |

| report_clock_properties                                                                                                                                                                                |     |

| Example                                                                                                                                                                                                |     |

| reset_sta                                                                                                                                                                                              |     |

| Example                                                                                                                                                                                                |     |

| ACE Tcl Commands                                                                                                                                                                                       | 610 |

|                                                                                                                                                                                                        |     |

| add_clock_preroute                                                                                                                                                                                     |     |

|                                                                                                                                                                                                        |     |

| add_clock_preroute                                                                                                                                                                                     | 610 |

| add_clock_prerouteadd_project_constraints                                                                                                                                                              |     |

| add_clock_preroute<br>add_project_constraints<br>Also See                                                                                                                                              |     |

| add_clock_preroute<br>add_project_constraints<br><i>Also See</i><br>add_project_ip                                                                                                                     |     |

| add_clock_preroute<br>add_project_constraints<br><i>Also See</i><br>add_project_ip<br>add_project_netlist                                                                                              |     |

| add_clock_preroute<br>add_project_constraints<br><i>Also See</i><br>add_project_ip<br>add_project_netlist<br>add_project_source_files                                                                  |     |

| add_clock_preroute<br>add_project_constraints<br><i>Also See</i><br>add_project_ip<br>add_project_netlist<br>add_project_source_files<br>add_region_find_insts                                         |     |

| add_clock_preroute<br>add_project_constraints<br><i>Also See</i><br>add_project_ip<br>add_project_netlist<br>add_project_source_files<br>add_region_find_insts<br>add_region_insts                     |     |

| add_clock_preroute<br>add_project_constraints<br><i>Also See</i><br>add_project_ip<br>add_project_netlist<br>add_project_source_files<br>add_region_find_insts<br>add_region_insts<br>apply_highlights |     |

| clear_arcs                  | 616 |

|-----------------------------|-----|

| clear_drawing               | 616 |

| clear_flow                  | 617 |

| clear_lines                 | 617 |

| clear_ovals                 | 617 |

| clear_polygons              | 617 |

| clear_rectangles            | 617 |

| clear_strings               | 618 |

| clock_info                  | 618 |

| clock_relation              | 619 |

| create_boundary_pins        | 620 |

| create_equivalent_regions   | 620 |

| create_flow_step            |     |

| create_impl                 | 622 |

| create_option_sets          | 622 |

| create_path                 | 623 |

| create_project              | 623 |

| create_region               | 624 |

| deselect                    | 625 |

| disable_flow_step           | 626 |

| disable_project_constraints | 626 |

| disable_project_source_file | 627 |

| display_file                | 627 |

| display_netlist             | 628 |

| display_properties          | 628 |

| draw_arc                    | 628 |

| draw_line                    |     |

|------------------------------|-----|

| draw_oval                    |     |

| draw_polygon                 |     |

| draw_rectangle               | 632 |

| draw_string                  | 633 |

| enable_flow_step             |     |

| enable_project_constraints   |     |

| enable_project_source_file   |     |

| export_all_partitions        |     |

| export_partition             |     |

| filter                       |     |

| find                         |     |

| generate_ioring_design_files |     |

| generate_ip_design_files     |     |

| generate_route_delay_table   |     |

| get_ace_cputime              |     |

| get_ace_current_memory_usage |     |

| get_ace_ext_dir              |     |

| get_ace_ext_lib              |     |

| get_ace_peak_memory_usage    |     |

| get_ace_version              |     |

| get_active_impl              |     |

| Example                      |     |

| Also See                     |     |

| get_active_project           |     |

| get_best_multiprocess_impl   |     |

| get_clock_region_bounds                  | 644   |

|------------------------------------------|-------|

| get_clock_regions                        | 644   |

| get_clock_type                           | 644   |

| get_compatible_ordering_codes            | 644   |

| get_compatible_placements                | . 645 |

| get_current_design                       | . 645 |

| get_current_partname                     | . 645 |

| get_efd_file_path                        | . 645 |

| get_enabled_constraints                  | . 646 |

| get_enabled_source_files                 | . 646 |

| get_fabricdb_path                        | 647   |

| get_file_line                            | 647   |

| get_flow_steps                           | 647   |

| get_impl_names                           | 647   |

| get_impl_option                          | . 648 |

| get_impl_option_is_supported             | . 648 |

| get_impl_option_is_supported_and_enabled | . 649 |

| get_inst_partition                       | . 649 |

| get_inst_region                          | . 650 |

| get_installation_directory               | . 650 |

| get_location                             | . 650 |

| get_noc_children                         | . 650 |

| get_noc_info                             | 651   |

| get_package_names                        | 651   |

| get_part_names                           | 651   |

| get_partition_changed                    | 652   |

| get_partition_force_changed                 | 652 |

|---------------------------------------------|-----|

| get_partition_info                          | 652 |

| get_partition_insts                         | 653 |

| get_partition_names                         | 653 |

| get_partition_timestamp                     | 653 |

| get_partition_type                          | 653 |

| get_path_ids                                | 654 |

| get_path_property                           | 654 |

| get_placement                               | 654 |

| get_project_constraint_files                | 655 |

| get_project_directory                       | 655 |

| get_project_ip_files                        | 655 |

| get_project_names                           | 655 |

| get_project_netlist_files                   |     |

| get_project_option                          |     |

| get_project_option_is_supported             |     |

| get_project_option_is_supported_and_enabled | 657 |

| get_project_output_directory                | 657 |

| get_project_source_files                    | 657 |

| get_properties                              |     |

| get_property                                |     |

| get_pvt_corners                             | 659 |

| get_region_bounds                           | 659 |

| get_region_insts                            |     |

| get_regions                                 |     |

| get_report_sweep_temperature_corners        |     |

| get_selection                |     |

|------------------------------|-----|

| get_synprj_from_netlist      |     |

| get_synprj_from_project      |     |

| get_techlib_name             |     |

| get_techlib_path             |     |

| get_techlibdb_path           |     |

| get_techlibt_name            |     |

| get_techlibt_path            | 663 |

| get_techlibx_name            |     |

| get_techlibx_path            |     |

| get_worst_path               |     |

| has_ace_ext_lib              |     |

| has_partitions               |     |

| highlight                    |     |

| ignore_cancel                |     |

| import_synplify_project_file |     |

| initialize_flow              |     |

| insert_delay                 |     |

| is_impl_option_enabled       |     |

| is_incremental_compile       |     |

| is_labmode                   |     |

| is_project_option_enabled    |     |

| is_timing_met                |     |

| load_flowscripts             |     |

| load_noc_info                |     |

| load_project                 |     |

| message                        |     |

|--------------------------------|-----|

| move_project_constraints       |     |

| move_project_netlists          | 670 |

| move_project_source_file       | 670 |

| move_relative_paths            |     |

| optimize_tile                  |     |

| redirect                       | 672 |

| refresh_drawing                | 672 |

| regenerate_all_ip_design_files | 672 |

| remap_partial_bitstream        | 672 |

| remove_clock_preroute          | 673 |

| remove_flow_step               | 674 |

| remove_impl                    | 674 |

| remove_path                    | 674 |

| remove_project                 | 674 |

| remove_project_constraints     | 675 |

| remove_project_constraints_pvt | 675 |

| remove_project_ip              | 675 |

| remove_project_netlist         | 676 |

| remove_project_source_files    | 676 |

| remove_region                  |     |

| remove_region_insts            |     |

| rename_impl                    | 678 |

| report_clock_regions           | 678 |

| report_clocks                  | 679 |

| report_coverage                | 679 |

| report_design_stats        |  |

|----------------------------|--|

| report_impl_options        |  |

| report_partitions          |  |

| report_performance         |  |

| report_pins                |  |

| report_placement           |  |

| report_power               |  |

| report_project_options     |  |

| report_routing             |  |

| report_utilization         |  |

| reset_impl_option          |  |

| reset_project_option       |  |

| restore_impl               |  |

| restore_project            |  |

| run                        |  |

| run_fanout_control         |  |

| run_final_drc_checks       |  |

| run_fpga_download          |  |

| run_generate_bitstream     |  |

| run_generate_final_reports |  |

| run_generate_fullchip_sim  |  |

| run_generate_netlist       |  |

| run_insert_holdbuffers     |  |

| run_multiprocess           |  |

| run_multiprocess_iterator  |  |

| run_place                  |  |

| set_equivalent_pins                                |     |

|----------------------------------------------------|-----|

| set_flyline_direction                              |     |

| set_impl_option                                    | 712 |

| set_max_flyline_fanout                             | 712 |

| set_partition_force_changed                        | 712 |

| set_partition_info                                 | 713 |

| set_placement                                      | 714 |

| set_project_constraints_pvt                        | 714 |

| set_project_option                                 | 715 |

| set_property                                       | 715 |

| set_region_bounds                                  |     |

| set_region_type                                    | 717 |

| set_units                                          | 717 |

| sleep                                              | 717 |

| source_encrypted                                   | 717 |

| source_secure                                      |     |

| trace_connections                                  |     |

| untar                                              |     |

| write_aeskey_efuse_bitstream                       |     |

| write_bitstream                                    | 720 |

| write_critical_paths_script                        | 721 |

| write_netlist                                      | 721 |

| write_partition_blackbox                           |     |

| write_partition_db                                 |     |

| write_tcl_history                                  |     |

| Tcl Commands for the IP Generator Plugin Framework | 723 |

| add_ip_binary_property    |  |

|---------------------------|--|

| Description               |  |

| Example                   |  |

| add_ip_bool_property      |  |

| Description               |  |

| Example                   |  |

| add_ip_enum_property      |  |

| Description               |  |

| Example                   |  |

| add_ip_file_path_property |  |

| Description               |  |

| Example                   |  |

| add_ip_float_property     |  |

| Description               |  |

| Example                   |  |

| add_ip_gui_control        |  |

| Description               |  |

| Example                   |  |

| add_ip_gui_group          |  |

| Description               |  |

| Example                   |  |

| add_ip_gui_page           |  |

| Description               |  |

| Example                   |  |

| add_ip_hex_property       |  |

| Description               |  |

| Example                   |  |

|                           |  |

| add_ip_include_path         | 731 |

|-----------------------------|-----|

| Description                 |     |

| Example                     |     |

| add_ip_int_property         | 732 |

| Description                 | 733 |

| Example                     | 733 |

| add_ip_label                | 733 |

| Description                 | 733 |

| Example                     | 733 |

| add_ip_output_file          |     |

| Description                 | 734 |

| Example                     | 734 |

| add_ip_output_file_group    |     |

| Description                 | 735 |

| Example                     | 735 |

| add_ip_port                 | 735 |

| Description                 |     |

| Example                     |     |

| add_ip_rule_message         | 736 |

| Description                 |     |

| Example                     |     |

| add_ip_signal_name_property |     |

| Description                 |     |

| Example                     |     |

| add_ip_string_property      | 737 |

| Description                 |     |

| Example                     |     |

| add_ip_to_gui              | 738 |

|----------------------------|-----|

| Description                |     |

| Example                    |     |

| create_ip                  |     |

| Description                |     |

| Example                    |     |

| get_ip_include_paths       |     |

| Description                |     |

| Example                    |     |

| get_ip_macro_name          | 740 |

| Description                |     |

| Example                    |     |

| get_ip_ports               | 740 |

| Description                |     |

| Example                    |     |

| get_ip_property_attributes |     |

| Description                |     |

| Example                    |     |

| get_ip_property_value      |     |

| Description                |     |

| Example                    |     |

| remove_ip_gui_control      |     |

| Description                |     |

| Example                    |     |

| remove_ip_gui_group        |     |

| Description                |     |

| Example                    |     |

| remove_ip_gui_page    |     |

|-----------------------|-----|

| Description           | 745 |

| Example               | 745 |

| remove_ip_label       | 745 |

| Description           |     |

| Example               |     |

| remove_ip_property    |     |

| Description           |     |

| Example               |     |

| send_ip_definitions   |     |

| Description           |     |

| Example               |     |

| send_ip_gui_update    |     |

| Description           |     |

| Example               |     |

| set_ip_category       |     |

| Description           |     |

| Example               |     |

| set_ip_description    |     |

| Description           |     |

| Example               |     |

| set_ip_macro_name     |     |

| Description           |     |

| Example               |     |

| set_ip_property_value |     |

| Description           |     |

| Example               |     |

|                       |     |

| set_ip_property_verilog_param_attributes |     |

|------------------------------------------|-----|

| Description                              |     |

| Example                                  |     |

| set_ip_resource_count                    | 750 |

| Description                              |     |

| Example                                  |     |

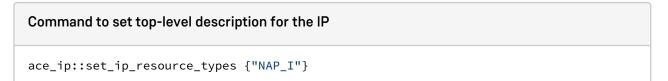

| set_ip_resource_types                    | 751 |

| Description                              |     |

| Example                                  |     |

| set_update_ip_configuration_callback     |     |

| Description                              | 752 |

| Example                                  | 752 |

| update_ip_binary_property                |     |

| Description                              |     |

| Example                                  |     |

| update_ip_bool_property                  |     |

| Description                              |     |

| Example                                  |     |

| update_ip_configuration                  | 756 |

| Description                              |     |

| Example                                  |     |

| update_ip_enum_property                  |     |

| Description                              |     |

| Example                                  |     |

| update_ip_file_path_property             | 758 |

| Description                              |     |

| Example                                  |     |

| update_ip_float_property                         | 758 |

|--------------------------------------------------|-----|

| Description                                      |     |

| Example                                          |     |

| update_ip_hex_property                           | 759 |

| Description                                      |     |

| Example                                          |     |

| update_ip_int_property                           | 759 |

| Description                                      |     |

| Example                                          |     |

| update_ip_label                                  |     |

| Description                                      |     |

| Example                                          |     |

| update_ip_signal_name_property                   |     |

| Description                                      |     |

| Example                                          |     |

| update_ip_string_property                        |     |

| Description                                      |     |

| Example                                          |     |

| Chapter 6 : Troubleshooting                      | 762 |

| ACE Exit Error Codes                             |     |

| Duplicate Names for Arrays                       |     |

| Clock Definitions/Constraints                    |     |

| Asynchronous Reset of I/O from the Core          |     |

| Multi-process Functionality License Requirements |     |

| Non-ASCII Characters in Path                     |     |

| Unable to Load Project: Project is Locked765                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Changing ACE Font Sizes766                                                                                                          |

| Fonts in Views                                                                                                                      |

| Linux:                                                                                                                              |

| Windows:                                                                                                                            |

| Fonts in HTML Reports76                                                                                                             |

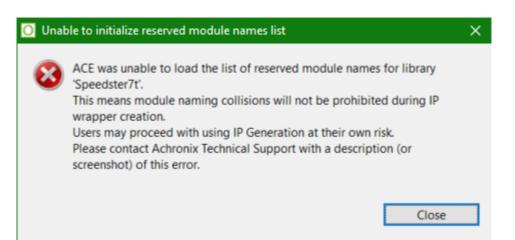

| Unable to Initialize Reserved Module Name List76                                                                                    |

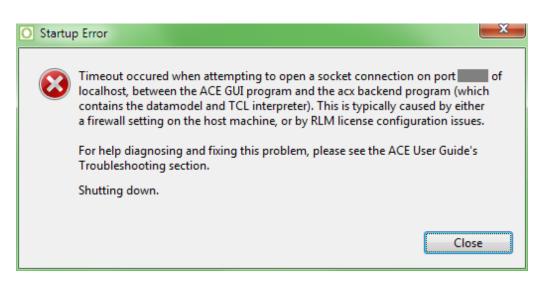

| Startup Error — ACE is Unable to Connect on Port NNNN of Localhost                                                                  |

| To Determine the Root Cause769                                                                                                      |

| If it is a Firewall Problem                                                                                                         |

| If it is a Licensing Problem770                                                                                                     |

| If it is a Filesystem or Network Performance Problem77                                                                              |

| Unexpected ACE GUI problem: java.lang.NoClassDefFoundError: com/achronix/api/<br>APIPlugin                                          |

| If the problem persists after -clean, or if the command prompt is unfamiliar                                                        |

| Detailed instructions:77.                                                                                                           |

| Multiprocess Summary Report Shows "No Timing Results Found" for Successfully<br>Run Implementations with Existing Timing Reports773 |

| Windows: ACE Incorrectly Reports Read/Write File Permission Problems                                                                |

| Windows: ACE GUI Shown as "Not Responding"773                                                                                       |

| Windows: Garbage sometimes appears in the Floorplanner View during panning operations (and remains after panning is completed)      |

| Windows: ACE Startup Error Due to Missing DLL Component in Windows 10774                                                            |

| Windows: The icons and buttons in ACE are too small775                                                                              |

| Asking Windows to upscale images and fonts for all applications                                                                     |

| As     | sking just ACE to upscale images and fonts                                                                                                                             | 775 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | Asking Windows to alter the scaling settings for just ACE (which may make text and fonts blurn blocky)                                                                 |     |

|        | Enabling ACE's application framework's fractional scaling (fonts remain crisp, but icons may become blurry and ACE may experience instability with some video drivers) | 777 |

|        | Resource Limits: ACE Reports an OutOfMemory Error, But There is Plent<br>Memory Available                                                                              | -   |

|        | : In the TWM Window Manager, the First Time the ACE GUI is Started Afte<br>lation, the ACE Window is So Small Users Might Not See it                                   |     |

|        | : Odd Behavior When Using X DISPLAY Forwarding if the X Client and X Se<br>lore than One Major Revision Apart                                                          |     |

| Linux: | ACE Menus Do Not Show Icons Next to the Action Names                                                                                                                   | 779 |

| Linux: | ACE Ignores LD_LIBRARY_PATH                                                                                                                                            | 779 |

|        | ACE forces the use of the GDK X11 rendering engine even while running<br>Wayland                                                                                       | 779 |

| Linux: | Incompatible Default Web Browser                                                                                                                                       | 780 |

| So     | olution                                                                                                                                                                | 781 |

|        | Details                                                                                                                                                                | 781 |