Test & Measurement

Test and Measurement tends to be at the leading edge of innovation as older approaches to test new technologies is not practical for technical and cost reasons. Like testers, FPGAs have often been the platform enabler for initial prototyping and deployment for Test and Measurement products. Some of the industries that demand high performance, tests for new and emerging standards and faster time to market includes Wired communications, 5G Infrastructure, IoT. Similarly the ATE testers need to support complex logic and memory components.

The Speedster7t FPGA family is optimized for high-bandwidth workloads and eliminates the performance bottlenecks associated with traditional FPGAs. Built on TSMC’s 7nm FinFET process, Speedster7t FPGAs feature a revolutionary new 2D network-on-chip (2D NoC), an array of new machine learning processors (MLPs) optimized for high-bandwidth and artificial intelligence/machine learning (AI/ML) workloads, high-bandwidth GDDR6 interfaces, 400G Ethernet and PCI Express Gen5 ports — all interconnected to deliver ASIC-level performance while retaining the full programmability of FPGAs.

Speedster7t Solution

Advanced FPGAs that provide the right blend of hardware programmable flexibility and very high bandwidth capability are ideal for test and measurement applications. In particular, Achronix’s Speedster7t FPGAs are especially well-suited to such application, which have challenging memory bandwidth requirements.

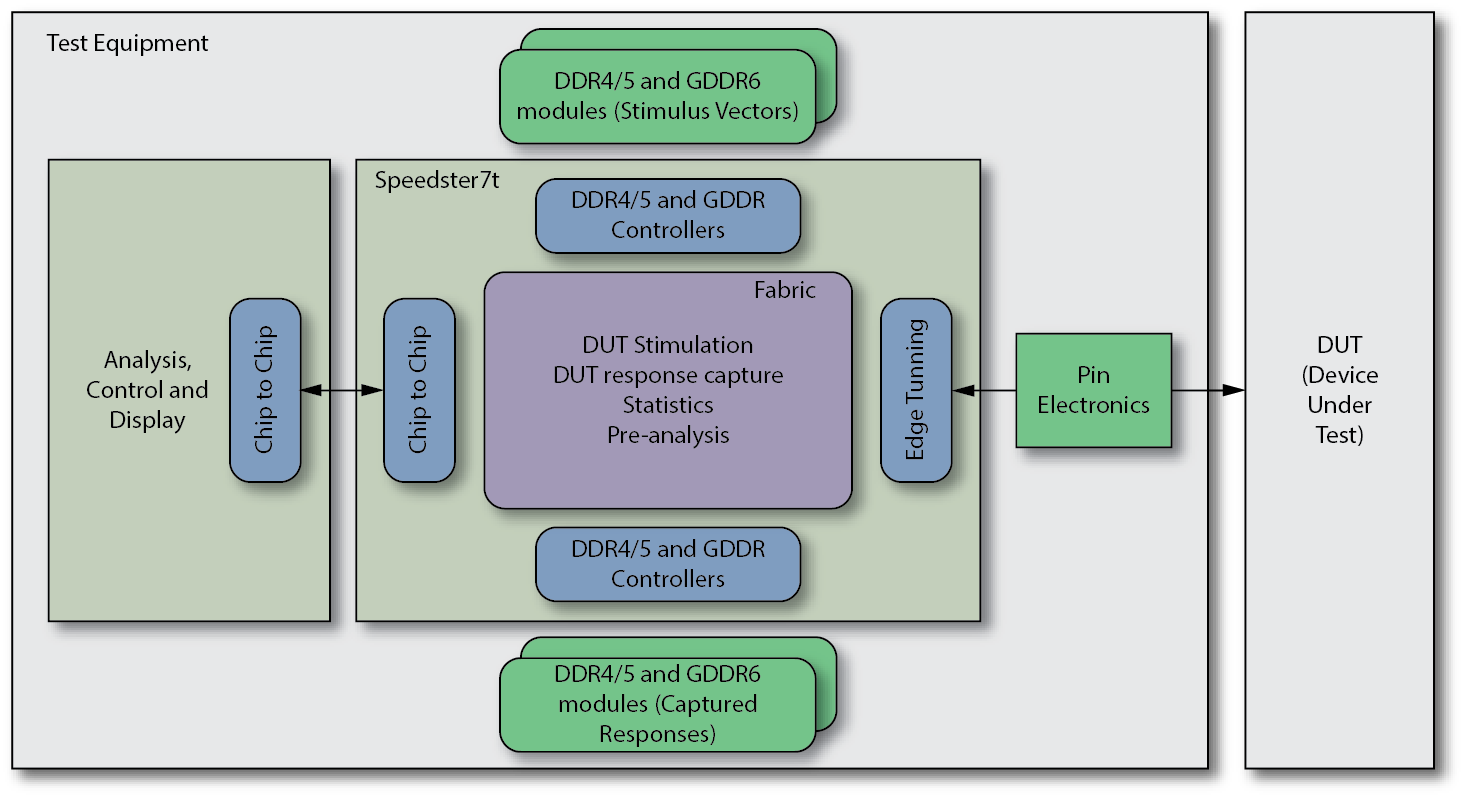

The block diagrams below illustrate value of high performance FPGAs in a ATE tester. These testers need very high bandwidth memories for buffering capture data. Speedster7t is the only FPGA in the industry that provides Terabits of bandwidth with GDDR6 memories at a fraction of cost of alternative HBM based FPGA solutions. The embedded GDDR6 hard controllers do not use any of the FPGA programmable resources. The GDDR6 memory bandwidth can be used for: 1) stimulus vector for data to be streamed to the system under test, and 2) captured responses of data retrieved from the SUT and stored for analysis.

In these applications, traffic is largely unidirectional and transferred in large contiguous blocks, maximizing the strengths of GDDR6 interface. Also these GDDR6 controllers are fully embedded as hardened IP blocks in the Speedster7t devices. Thus the FPGA can perform more tasks, potentially absorbing the functions of other devices-lowering devices count and complexity.

Speedster7t devices excel in memory capacity and bandwidth with 8 independent GDDR6 components or 16 independent GDDR6 channels that provide over 4 Tbps of memory bandwidth. They also provide up to 200 Mb of embedded RAM in the form of block and distributed RAM.

| Application Requirements | Speedster7t Value |

|---|---|

| Need for substantial external connectivity via PCIe and Ethernet |

|

| Highest memory bandwidth for buffering |

Memory hierarchy

|

| Wide data-path and high performance |

FPGA fabric optimized for high throughput data transfer and acceleration

|

| Substantial logic capacity to implement complex, custom algorithms |

Scalable family of devices up to 2.6M 6LUTs of logic |

| Substantial internal memory for queuing pointers, internal cache and scratchpad RAM | Up to 300 Mbits of internal SRAM |