Achronix and BigCat Wireless join forces to power the future of 5G/6G with FPGA-based solutions, optimizing MIMO, beamforming, and real-time processing for unmatched wireless performance.

Network operators face mounting pressure to expand their capabilities with the rollout of 5G and the impending arrival of 6G. Emerging technologies such as massive multiple input, multiple output (MIMO), spatial beamforming, and machine learning-based optimizations are becoming essential to achieve the speed, efficiency, and reliability expected of modern networks.

However, these advanced methods have their own computational challenges, necessitating a robust hardware foundation capable of handling vast data volumes while supporting flexible, real-time processing. That’s why Achronix recently collaborated with BigCat Wireless to introduce a solution that brings powerful FPGA-based processing and optimized DSP kernels to the forefront of 5G and beyond.

Achronix FPGA Architecture with Machine Learning Processors

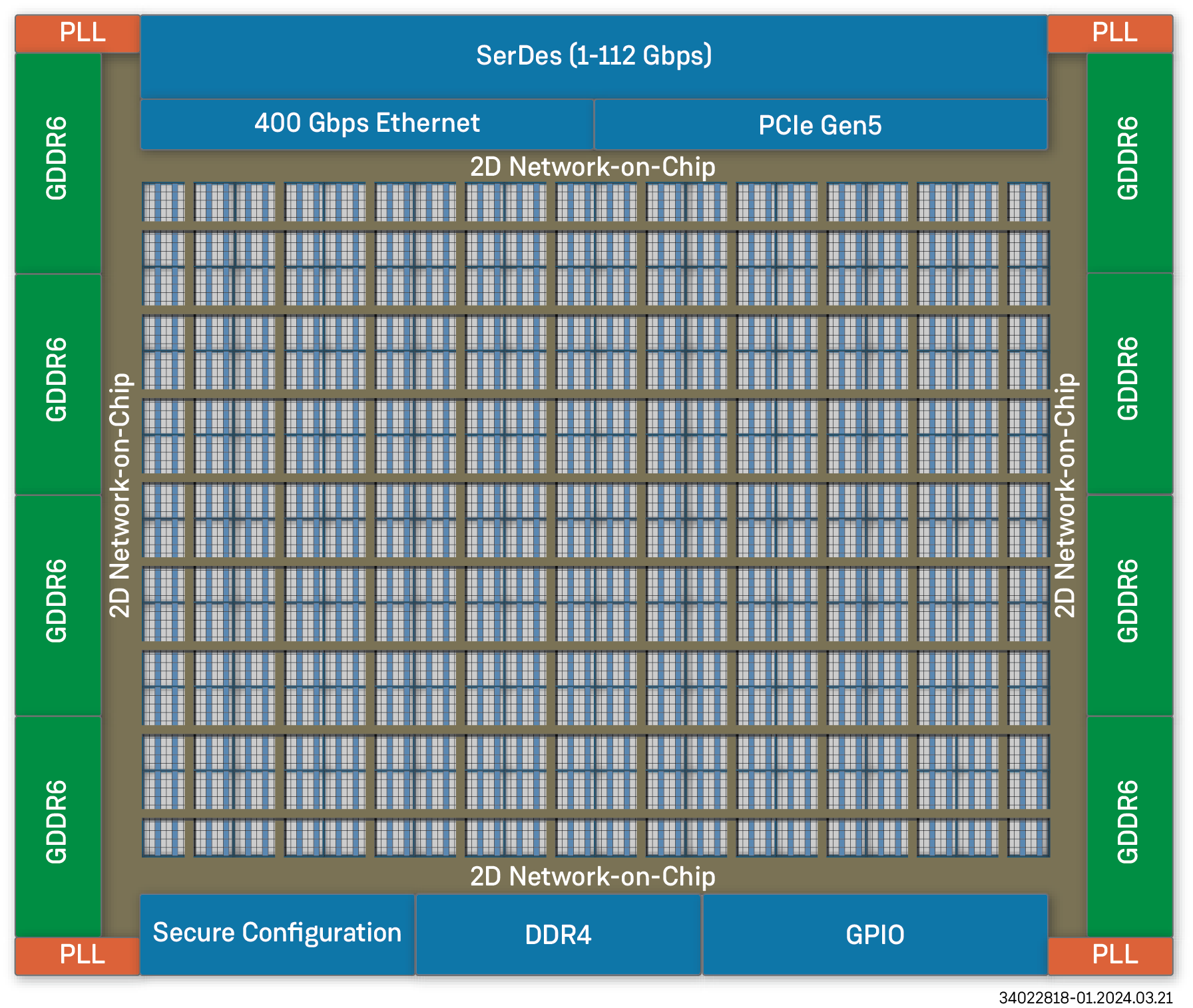

The Achronix contribution to this partnership is Speedster7t FPGAs, which integrate a revolutionary 2D network-on-chip (NoC) architecture and machine learning processors (MLPs) optimized for parallel processing.

The 2D NoC enables high-bandwidth data transfers between the FPGA fabric and external memory or I/O, with each node in the NoC directly connected to the MLPs. Consisting of a series of rows and columns spread across the FPGA fabric, the 2D NoC can provide greater than 20 Tbps of ultra-high bandwidth connectivity to external high-speed interfaces and routing data within the programmable logic fabric itself. Within this, each row or column has two 256-bit data paths that individually support 512 Gbps data rates.

Achronix Products Feature a Revolutionary 2D NoC

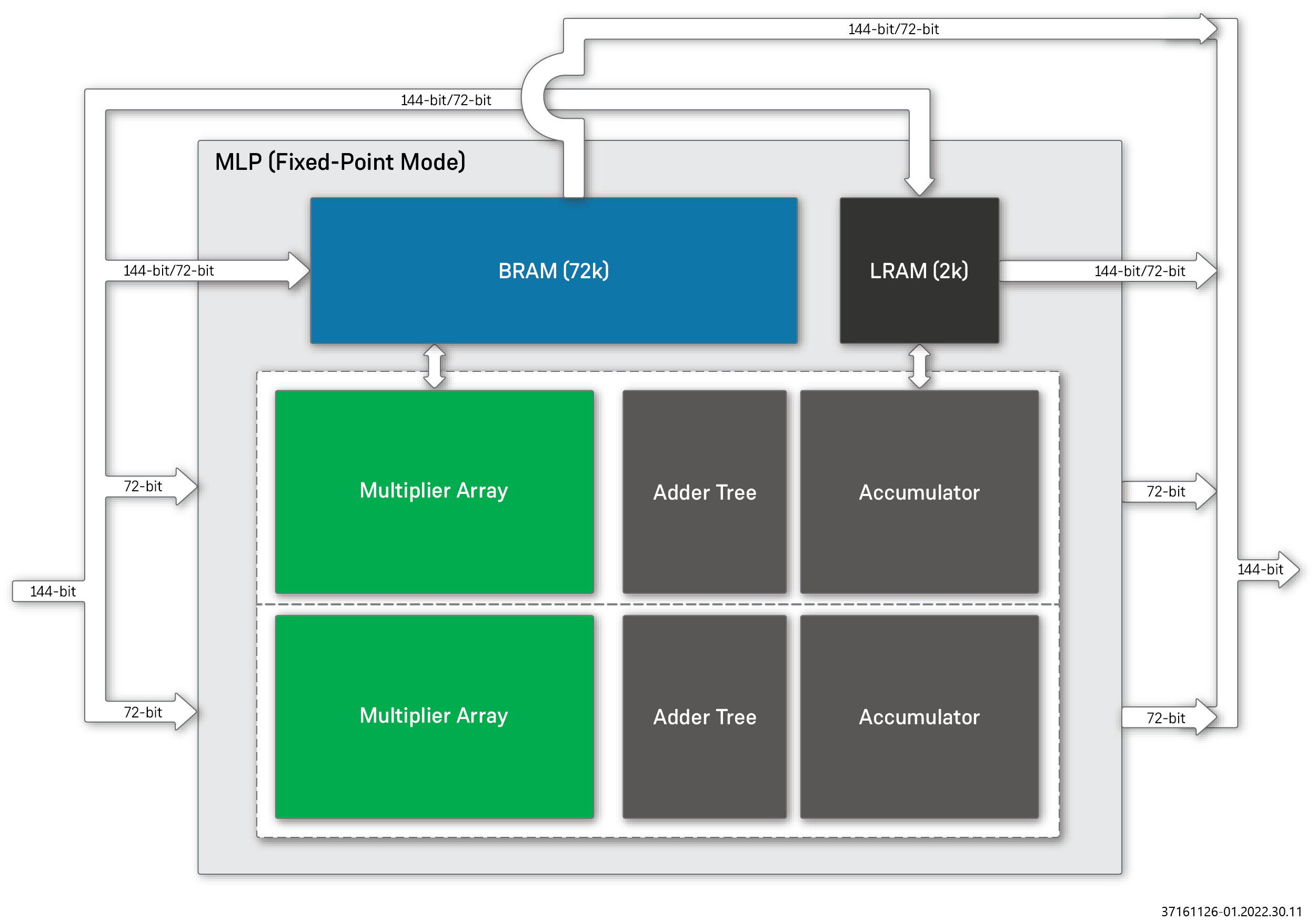

Meanwhile, the MLPs within the Speedster7t FPGA are tailored to perform complex computations at high speeds, specifically targeting high-performance DSP tasks such as beamforming and fast Fourier transforms (FFT). Each MLP contains a configurable array of multiply-accumulate (MAC) units capable of supporting fixed and floating-point operations. The Speedster7t family supports up to 40,960 int8 MACs, resulting in a theoretical maximum performance of 61.4 tera-operations per second when running at 750 MHz.

This architecture enables the parallel execution of signal processing algorithms in the 5G lower physical layer (PHY), such as efficiently handling multi-user MIMO configurations.

BigCat Wireless DSP IP for 5G Signal Processing

Complementing the hardware excellence of the Speedster7t FPGA is BigCat Wireless’ suite of DSP IP.

One of the differentiating features of BigCat’s DSP IP is its matrix multiplication kernel, capable of handling floating-point operations for matrix sizes up to 64 × 64. BigCat’s IP also supports configurable FFT/iFFT operations for frequency domain processing. For example, the IP allows for N-point FFT configurations ranging from 1K to 4K points, enabling adaptation to various 5G subcarrier spacings and bandwidths. With 5G’s variable channel bandwidth requirements, which can span from 5 MHz to 100 MHz depending on the deployment scenario, such flexibility is necessary.

FFT and FIR Filter Performance

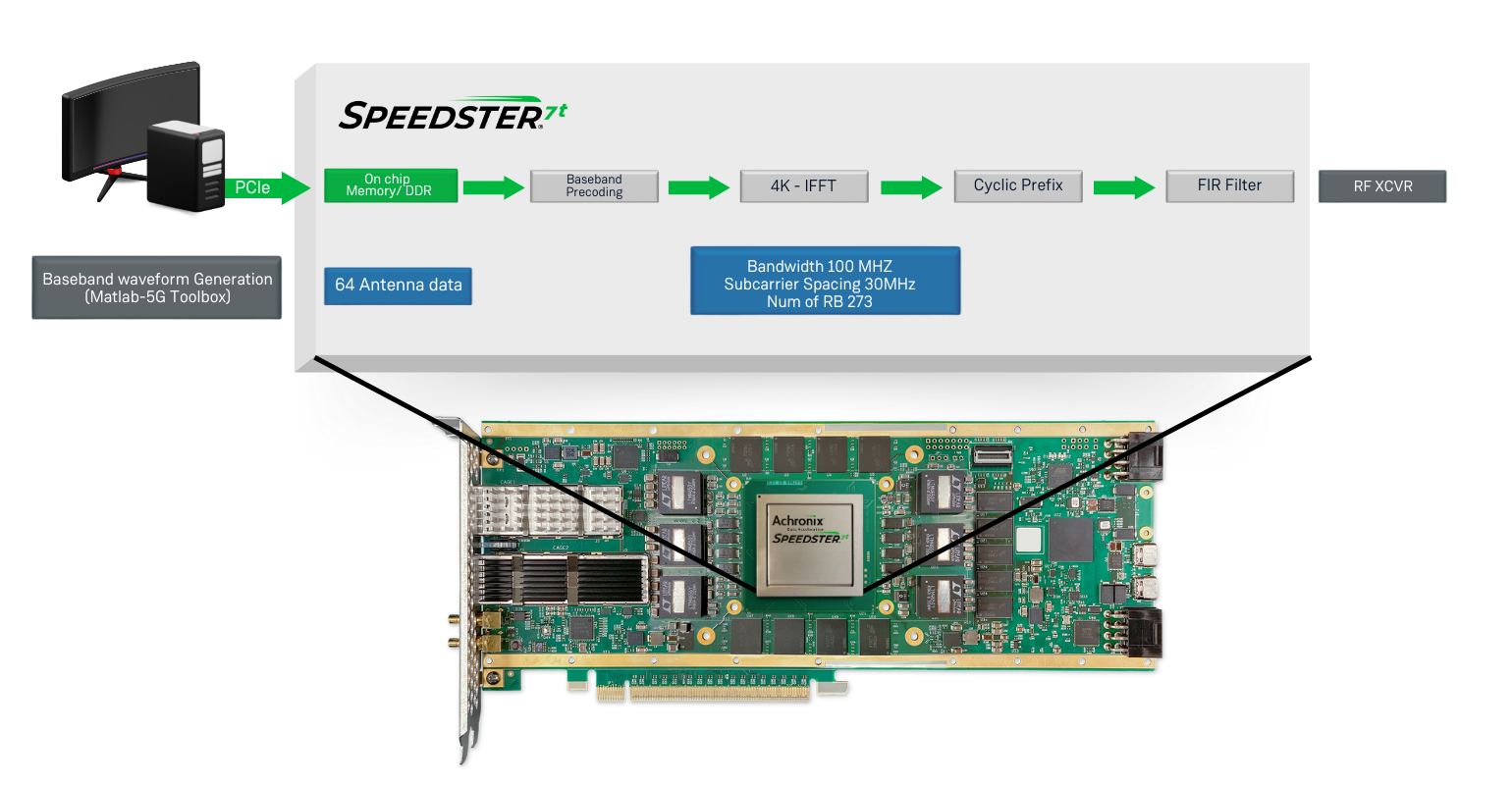

Our Speedster7t FPGAs and BigCat’s DSP IP combination have already demonstrated exceptional performance in handling FFT and FIR filter operations. The configurable N-point FFT enables high-speed processing of different bandwidths, subcarrier spacings, and OFDM symbol sizes.

The solution includes highly efficient Finite Impulse Response (FIR) filters, integral to tasks like channel filtering and noise reduction. These FIR filters support up to 128 taps for precisely filtering signals across a wide frequency range and are optimized for real-time processing, with coefficients stored in RAM for run-time reconfigurability. These features allow the system to dynamically adapt to changing network conditions for maximum system efficiency and reliability.

MLP-Optimized Parallel Processing for MIMO and Beamforming

Our joint solution is also well-suited for massive MIMO and spatial beamforming applications.

Massive MIMO relies on simultaneously transmitting multiple data streams from large antenna arrays. To manage these streams effectively, the system must calculate beamforming weights and apply them to each antenna element in real-time.

Achronix MLP in Fixed-Point Mode

In this context, the Achronix MLPs excel thanks to their ability to execute large numbers of matrix multiplications in parallel. By handling matrix operations for beamforming weight calculations with up to 64 × 64 matrix dimensions, the MLPs provide the computational muscle necessary for real-time, high-throughput MIMO processing. This parallelism significantly reduces the processing time for MIMO operations and allows the system to support more users and higher data rates.

BigCat’s DSP IP further enhances this capability by optimizing the beamforming algorithms to run efficiently on Achronix hardware. The IP includes specialized DSP kernels tuned to minimize latency while maximizing resource utilization so that the system can handle the intense computational demands of massive MIMO without exceeding power or resource budgets. A complete massive MIMO solution can be put together using BigCat Wireless DSP kernels optimized to leverage Achronix MLPs. The single chain in the figure below illustrates the ease with which a massive MIMO beamforming solution can be constructed using BigCat Wireless’ DSP kernels in the Achronix Speedster7t eFPGA.

Scalability and Customization for Future 6G Networks

While this partnership's current focus is on 5G, the technology is built with an eye toward future 6G networks, which are expected to demand even greater performance and flexibility. Our Speedster7t FPGA architecture is inherently scalable, allowing for future processing power and bandwidth upgrades. For example, the MLPs can be reconfigured to support new algorithms and higher computational loads.

The solution’s customizability also sets it apart from other offerings in the market. Telecommunications providers can use our solution to tailor the system to their needs, adjusting the balance between power consumption, latency, and computational throughput based on their network’s unique demands. This flexibility extends to integrating additional IP blocks, allowing providers to incorporate new features as they become necessary for 6G applications, such as self-interference cancellation and AI-driven network management.

Leading the Way in 5G and Beyond

As 5G and 6G become increasingly central to the wireless world, now is the time to explore the advantages of Achronix and BigCat’s cutting-edge solutions. By combining the power of our MLP-enabled Speedster7t FPGAs with BigCat’s DSP IP, our solution delivers industry-leading performance in computational throughput, latency, and flexibility. Our joint solution sets a new standard for efficiency and scalability in the wireless space for massive MIMO, beamforming, or other signal processing tasks.

Contact the Achronix sales team at sales@achronix.com or contact BigCat Wireless at bigcat@bigcatwireless.com.