Learn the basics about eFPGA IP, its benefits, and why it is becoming a crucial element for the future of advanced driver assistance systems (ADAS) technology.

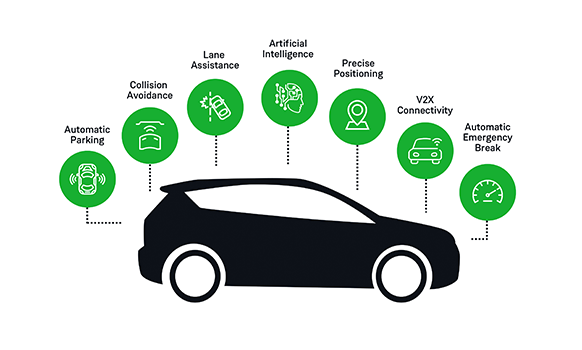

One of the major aspects of increasing vehicle electrification and autonomy is the proliferation of advanced driver-assistance systems (ADAS). These systems are quickly becoming present in almost all vehicles on the market today, and this trend is only expected to continue as the technology matures. However, as technology evolves, the hardware challenges facing ADAS designers are becoming increasingly complex. In this blog, we’ll look at the hardware requirements for ADAS, how FPGAs have historically filled these voids, and why eFPGA IP will be the next ADAS hardware trend.

Hardware Requirements for ADAS

The growth of ADAS in modern-day vehicles is resulting in some serious challenges for the underlying hardware. In a mission-critical application such as ADAS, the utmost important goal is to ensure the safety of the vehicle occupants. This goal requires systems to work accurately, reliably, and in real-time (i.e., low latency). At the same time, these systems need to operate at the lowest power consumption possible in order to preserve battery life and extend the EV range.

ADAS Places an Intense Strain on Compute Hardware

Balancing these requirements is a substantial challenge for ADAS since the systems tend to rely on extremely data and compute-intensive tasks such as machine learning algorithms. The result is ADAS hardware must acquire data, aggregate it via sensor fusion, run machine learning algorithms, and then take action — all in real-time and at the lowest power budget possible — clearly no easy feat.

The challenge is further coupled by the fact that automotive designers need a flexible and scalable hardware platform to meet the changes in the rapidly evolving specifications.

Hardware Acceleration and FPGAs

To solve the daunting challenges facing ADAS hardware, designers are adopting dedicated hardware accelerators to increase performance vs. traditional CPU-based architectures. By moving from more general computing resources such as CPUs or GPUs, dedicated hardware accelerators provide systems with improved performance and power efficiency for a specific application. Within this, the options generally fall between FPGAs and ASICs, with FPGAs providing the most flexibility and ASICs providing the highest performance.

A key feature of FPGAs is that they are able to offer high levels of parallelism while still being programmable for specific workloads. The result is that FPGAs have been shown to provide significant value in workload acceleration, especially in situations where performance and latency are key. Even further, FPGAs help systems balance the tradeoffs between performance and power efficiency by offering the best performance per watt for accelerating workloads compared to more general-purpose CPU and GPU-based systems.

Equally as important, FPGAs offer an advantage over ASICs in terms of scalability thanks to their programmable nature. This adaptability is particularly important in machine learning systems such as ADAS, where the underlying algorithms change at a rapid pace. Moreover, the specifications for ASICs must be defined years in advance, while FPGAs can be updated and reprogrammed at a minute’s notice. This feature enables FPGA-based ADAS systems to deliver a scalability and versatility that is simply unachievable with ASICs.

For these reasons and more, there are currently over 250 Million FPGAs in cars today, with over 75 million of those being used in ADAS applications.

Industry Trend: eFPGAs for ADAS

As powerful as hardware acceleration can be, devices such as FPGAs and ASICs often still can’t operate entirely on their own. Today’s ADAS solutions require the integration of hardware accelerators alongside a CPU, whose purpose is to handle many general-purpose and organizational tasks at the system level. It is for this reason that heterogeneous computing platforms such as SoCs have become among the most common in acceleration and ADAS platforms.

eFPGA Technology, such as Achronix Speedcore IP, can be Tightly Coupled with CPU Resources

Therefore, it’s our belief that the next major trend in ADAS computing will be the rise of embedded FPGA (eFPGA) IP in custom ASICs. With eFPGA IP, designers gain the ability to harness the benefits of FPGA technology while tightly coupling their hardware acceleration with other ASIC subsystems such as CPUs and I/O interfaces. By embedding the FPGA in a custom SoC alongside a CPU, eFPGA IP enables significant cost, power, and space savings compared to a discrete FPGA solution.

Specifically, our estimates show that eFPGA IP integration can help designers achieve 90% cost savings, 75% power reduction, 100× improvement in latency and a 10× increase in interface bandwidth as compared to standalone FPGA-based systems. Hence, ADAS will begin incorporating heterogeneous solutions based on the use of eFPGA technology in the near future.

Achronix’s Industry Role

Today, Achronix is the only company that produces both FPGA and eFPGA IP solutions in high-volume production. Thanks to flagship products such as our Speedcore eFPGA IP, we have empowered over 15 million eFPGA-based products in multiple industry segments to date. As the needs for ADAS computing grow and evolve, we feel well-positioned to support the changes and enable the next generation of computing platforms.