For anyone who has looked at new cars lately, it's hard not to notice how quickly automotive electronics are advancing. Looking at automotive safety technology from just three years ago vs. today, you see a significant increase in the number of cameras to support applications such as surround-view display, driver distraction monitors, stereo vision cameras, forward-facing and multiple rearview cameras. In addition to cameras, system capabilities have increased to include auto emergency braking, lane departure warning, rear blind-spot detection and traffic sign recognition.Thistrend suggests continued rapid innovation in automotive electronics, but also introduces new challenges to automotive OEMs including:

- How to rapidly develop new features and safety functionality when the average time to develop a new vehicle has been reduced from 48 months to around 24 months (see Shortening of Life Cycle and Complexity Impact on the Automotive Industry) while supporting a long, 10+ year, lifecycle?

- How to anticipate the hardware and software requirements that will be required when the platform architecture is decided years in advance of the vehicle availability?

- How to increase performance and quality that automotive customers are now come to expect when compared to what is available in consumer electronics?

The ASIC Solution

To help solve these problems, automotive OEMs need to rethink their system architecture and design it to include flexibility with the ability to make changes late in the design process and add ongoing features and capabilities. This redesigned system architecture allows OEMs to differentiate from other competitors plus deliver solutions to technical challenges not possible to solve using standard hardware components.

Traditionally the selection of the ADAS architecture components relied on off-the-shelf components designed to support specific automotive safety and environment requirements. For non-differentiated functionality, such as ABS, this approach is perfectly fine. However, if you are designing innovative safety features, many OEMs choose to build their own custom ASICs. Custom ASICs provide the lowest overall cost and highest performance versus any off-the-shelf component: however, ASICs introduce risk. If you do not identify all of the required functionality, you will be unable to change without a costly and time-consuming ASIC redesign.

Despite the inherent risks, one innovative automotive company, Tesla, has decided that the ASIC route is the best option for them to deliver advanced safety functionality. Tesla developed their own full, self-driving (FSD) ASIC for this purpose (see "Tesla Full Self Driving ASIC"). This development started in February 2016 and took 29 months until to July 2018 when the ASIC was production qualified. Tesla needed to decide on the required ASIC capabilities nearly three years before the vehicle shipped to customers. They decided on an architecture which included:

- Integrated camera interfaces running at 2.5G pix/sec

- 128-bit wide LPDDR4 memory

- Camera ISP

- H.265

- GPU supporting FP32 and FP16

- 12 ARM A72 CPUs.

Tesla FSD Architecture Board (at 1h18min)

Future-Proofing Hardware

However, what if the cameras they thought were going to be used were discontinued, new camera ISP is required for better low-light performance, or the GPU needed to support block floating point instead of FP32? These event could force an ASIC respin or major architecture change that would delay the future production of their vehicles. Wouldn't it be nice to build flexibility into this ASIC to allow adding these capabilities late in the design cycle to avoid an ASIC respin and delayed production availability?

Fast forward to 2020 where we now see automotive ASIC manufacturers addressing this challenge by developing novel ASIC architectures which include embedded FPGA (eFPGA) IP. While eFPGAs where not a mainstream technology back in 2016 when the Tesla FSD was developed, they are now. Achronix eFPGA IP is now in production in multiple high-volume applications, proving its ability to reach mainstream production. Now we are seeing eFPGA IP being adopted by automotive OEMs to embed hardware programmability to address the new challenges mentioned above.

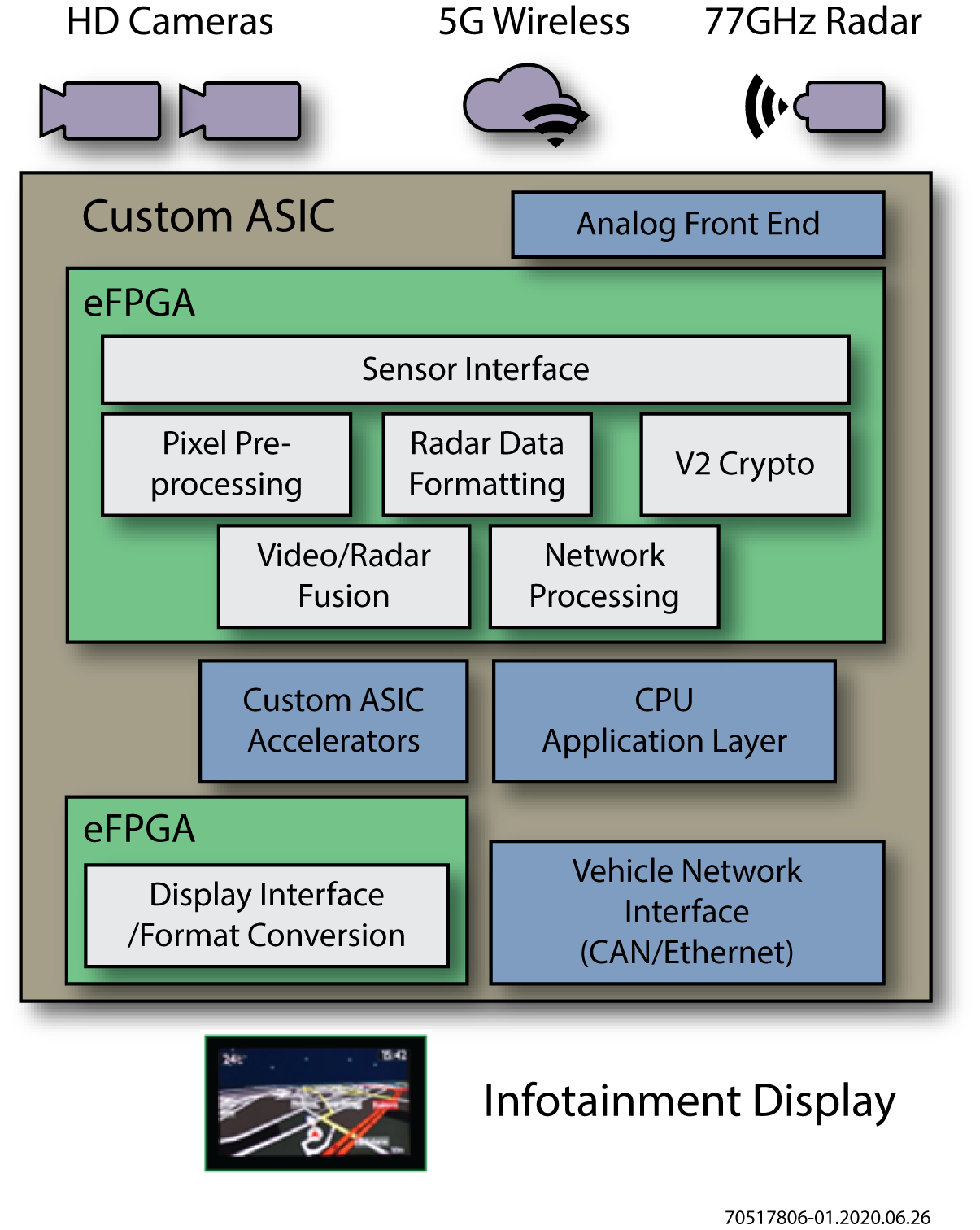

Unlike standalone FPGAs which are only available with specific logic density, memory, resource mix, and I/O interfaces, eFPGA IP solutions can be fully customized for the specific automotive workload. They offer up to 90% lower costs, and 75% lower power when compared to standalone FPGAs, while offering the same ability to add in new hardware functionality after the ASIC is developed. Examples are changing hardware specifications to deliver new innovative functionality required for enhanced radar and camera sensor fusion, new larger display technologies, and new image sensor capabilities. The block diagram below shows some of the capabilities of ASICs with integrated eFPGAs can deliver to automotive manufacturers.

eFPGA IP Based ADAS ASIC Architecture

This architecture is possible using Achronix's Speedcore eFPGA IP technology. Speedcore eFPGA IP provides a competitive advantage which allows for faster development time and the ability to add new and innovative features that can be defined after the ASIC hardware architecture is finalized. eFPGA IP is truly a game changer in the automotive world, and Achronix is excited to see what eFPGAs can bring to the future of automotive ASIC design. You can contact Achronix to learn more about our automotive solutions today.