| Blog Icon | Blog Title | |

|---|---|---|

|

What is an FPGA and Why the Answer is Changing?What is an FPGA? With the advent of new FPGA architectures, the answer has changed more in the last two years than ever before. Traditionally, an FPGA or field programmable gate array, is a reconfigurable semiconductor device comprising programmable logic gates and interconnect or routing, connected to multipurpose I/O pins. An FPGA can be reprogrammed to perform any function, and its functionality can be changed over time. (For a great summary and history of the FPGA industry and technology. |

> |

|

Insights from the Next FPGA Platform EventIt was exciting to participate in the Next FPGA Platform on January 22nd at the Glasshouse in San Jose. I found it was particularly exciting to have Achronix share in a panel discussion with Xilinx and Intel. The Next Platform co-editors Nicole Hemsoth and Timothy Prickett Morgan did a great job in interviewing experts from FPGA ecosystem with insightful questions. The best part of Next Platform events is their format, where they keep marketing pitches to minimum with no presentations, just discussions. I will summarize a few insights and observations from the event. |

> |

|

FPGAs in the 2020s – The New Old ThingFPGAs are the new old thing in semiconductors today. Even though FPGAs are 35 years old, the next decade represents a growth opportunity that hasn’t been seen since the early 1990s. Why is this happening now? |

> |

|

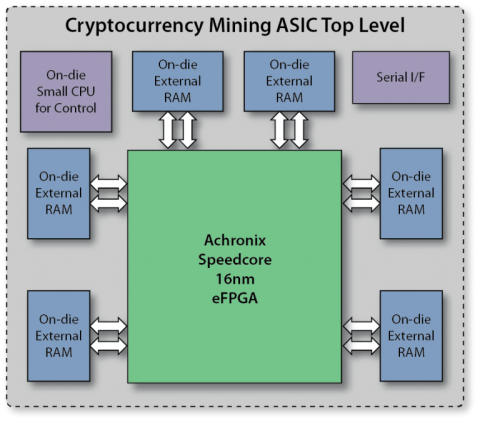

Mine Cryptocurrencies Sooner Part 3New, post-Bitcoin cryptocurrencies have been developed with ASIC resistance to level the competitive playing field for cryptocurrency miners, as discussed in parts 1 and 2 of this blog. ASIC resistance was developed to counteract monopolization of cryptocurrencies by the few entities that can afford to build ASIC solutions, as has happened with Bitcoin. However, ASIC resistance does not ensure the necessary scarcity of a cryptocurrency. |

> |

|

Mine Cryptocurrencies Sooner Part 2Bitcoin has lost much of its allure due to the concentration of control of the world’s Bitcoin mining resources by a few players in a few locations, as discussed in Part 1 of this blog. In response, the larger, global cryptocurrency community has started to develop alternative cryptocurrencies based on lessons learned from the Bitcoin experience. |

> |

|

Mine Cryptocurrencies Sooner Part 1Cryptocurrency mining is the process of computing a new cryptocurrency unit based on all the previously found ones. The concept of cryptocurrency is nearly universally recognized by the publicity of the original cryptocurrency, Bitcoin. Cryptocurrencies were supposed to be a broadly democratic currency vehicle not controlled by any one entity, such as banks, governments, or small groups of companies. Much of a cryptocurrency’s acceptance and trustworthiness is based on that proposition. However, with Bitcoin, that is not how it unfolded. |

> |

|

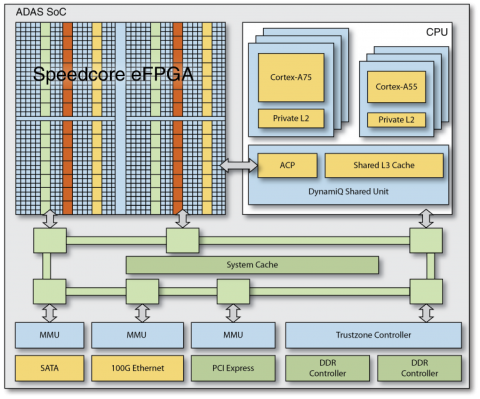

How to Meet Self-Driving Automotive Design Goals Part 2Today, the advanced driver-assistance systems (ADAS) processor market is growing by more than 25% per year. This growth is driven by the migration of ADAS features – including automatic emergency braking, lane-changing assist, and adaptive cruise-control functions – from luxury vehicles to midrange and even entry-level vehicles. ADAS features will be almost universal by the middle of the next decade. |

> |

|

How to Meet Self-Driving Automotive Design Goals Part 1Achronix anticipates that the favored self-driving architecture of the future will be increasingly decentralized. However, both the centralized and decentralized architectural design approaches will require hardware acceleration in the form of far more lookaside coprocessing than is currently realized. |

> |

|

Speedcore eFPGAs are an Enabling Technology for 360° Surround-view SystemsNext-generation video applications such as surveillance, object detection, motion analysis now rely on 360° embedded vision. In these systems, multiple real-time camera streams (up to six) are processed together frame by frame, with each frame corrected for distortion and other image artifacts, adjusted for exposure and white balance, and then stitched together dynamically into a single 360° panoramic view, then output at 4K 60 fps and ultimately projected on a spherical coordinate space. |

> |