| Blog Icon | Blog Title | |

|---|---|---|

|

Achronix’s Next-Generation, 7nm FPGA Family Will Feature Micron’s Blazingly Fast GDDR6 Memory – To 4 Tbps and BeyondMicron Technology announced today that its high-performance GDDR6 SDRAM (in volume production since June) will be the high-speed memory of choice for Achronix’s yet-to-be-announced, next-generation FPGA family, making Achronix the world’s first FPGA vendor with announced GDDR6 support. |

> |

|

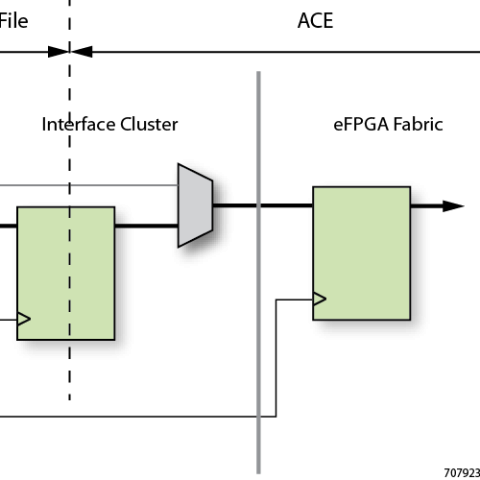

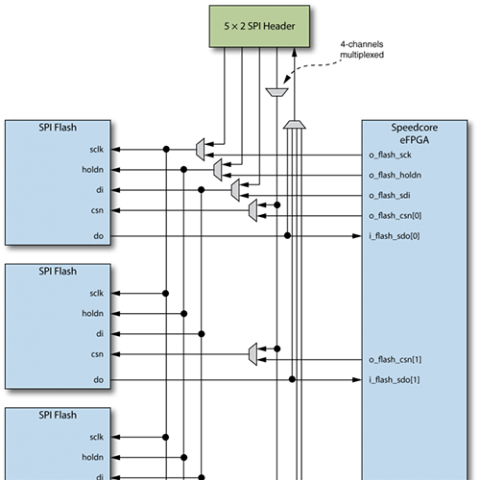

Learning to Share - Embedded FPGA Timing ClosureWhen we start school as young children, one of the first lessons we learn is how to share (followed quickly by not running with scissors). As our Sr. Director of Systems Engineering, Kent Orthner, discussed at DAC this past June, sharing is also key when it comes to closing timing with embedded FPGAs (eFPGAs). With an eFPGA such as Speedcore IP, the task of closing timing is owned by two people: the ASIC designer, responsible for the design in the host ASIC, and the FPGA designer, responsible for the design targeting the FPGA. |

> |

|

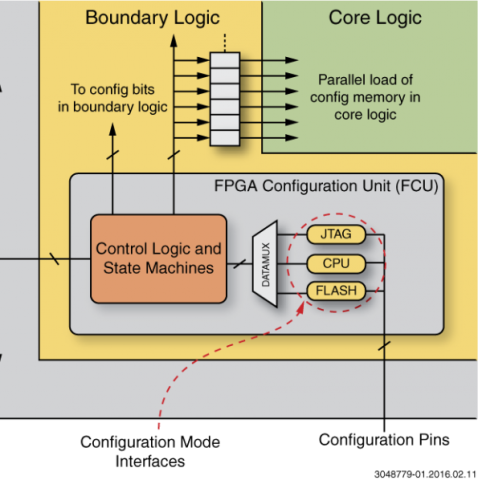

Configuring Your Speedcore eFPGA, Part 2: Configuration TimeAs discussed in part 1 of this blog post, each instance of an Achronix Speedcore eFPGA in your ASIC or SoC design must be configured after the system powers up because Speedcore eFPGAs employ nonvolatile SRAM technology to store its configuration bits. The time required to program a bitstream into a Speedcore eFPGA depends on the configuration mode being used, the data width, clock frequency, and of course, the size of the configuration bitstream. |

> |

|

Configuring your Speedcore eFPGA, Part 1: Configuration InterfacesEach instance of an Achronix Speedcore eFPGA in your ASIC or SoC design must be configured after the system powers up because Speedcore eFPGAs employ nonvolatile SRAM technology to store the eFPGA’s configuration bits. Each Speedcore instance contains its own FPGA configuration unit (FCU) that initializes, configures, and manages the Speedcore eFPGA’s core logic array. For example, if you instantiate three Speedcore eFPGAs in your ASIC/SoC design, there will be three FCUs on the chip. |

> |

|

How Big Should your eFPGA be? Here are Some Hints.Once you’ve made the correct decision to add Speedcore eFPGA IP to your ASIC or SoC design, the next question you’ll need to answer is how large to make the eFPGA. That’s a multi-dimensional question because Speedcore eFPGAs contain many types of blocks including: |

> |

|

When, Why, and How Should You Use Embedded FPGA Technology for Hardware Acceleration?If integrating an embedded FPGA (eFPGA) into your ASIC or SoC design strikes you as odd, it shouldn’t. ICs have been absorbing almost every component on a circuit board for decades, starting with transistors, resistors, and capacitors — then progressing to gates, ALUs, microprocessors, and memories. FPGAs are simply one more useful component in the tool box, available for decades as standalone products, and now available for integration into your IC design using the Achronix Speedcore eFPGA, supported by Achronix ACE design tools. |

> |

|

My Path to Achronix Applications EngineeringGrowing up in Virginia, I never thought I would become an engineer. Not that I didn’t want to be an engineer — the thought just never crossed my mind. As a kid, I spent most of my free time pursuing various arts. I loved music, learning to play the flute, piccolo, and later the electric bass, on top of spending many years studying classical ballet. And it may not be considered art, but I also loved baking; the process of perfecting old recipes and the creativity of coming up with new ones. |

> |

|

Speedcore eFPGAs as a Risk MitigatorSystem architects and program managers worry about how to mitigate risk when developing an SoC. Risk can present itself in many forms, but it is most commonly the result of ill-defined and changing standards as well as the need to future-proof designs. |

> |

|

Moving Machine Learning off the Cloud Calls for eFPGAsArtificial intelligence is reshaping the world we live in and opening opportunities in commercial and industrial systems applications that range from autonomous driving and medical diagnostics to home appliances, industrial automation, adaptive websites and financial analytics. Next up is the communications infrastructure that links systems together, moving toward automated self-repair and optimization. For example, the U.S. |

> |